# RF POWER AMPLIFIER TECHNIQUES FOR SPECTRAL EFFICIENCY AND SOFTWAREDEFINED RADIO

Rameswor Shrestha

#### **Graduation committee:**

Chairman and Secretary

Prof. dr. ir. A.J. Mouthaan University of Twente

Promotor

Prof. dr. ir. B. Nauta University of Twente

Assistant Promotor

Dr. ir. R. van der Zee University of Twente

Members

Technische Universiteit Delft Prof. dr. J.R. Long

Prof. dr. ir. A.J.M. van Tuijl University of Twente Prof. dr. ir. F.E. van Vliet University of Twente Dr. A. Cathelin **STMicroelectronics**

Title: RF POWER AMPLIFIER TECHNIQUES FOR SPECTRAL

EFFICIENCY AND SOFTWARE-DEFINED RADIO

Rameswor Shrestha Author: ISBN:

978-90-365-3076-7

ISSN: 1381-3617 (CTIT Ph.D. thesis series No. 10-175)

©2010 Rameswor Shrestha All rights reserved.

This work was supported by NXP Semiconductors (former Philips Semiconductors) in Nijmegen, The Netherlands

# RF POWER AMPLIFIER TECHNIQUES FOR SPECTRAL EFFICIENCY AND SOFTWARE-DEFINED RADIO

#### **DISSERTATION**

to obtain

the degree of doctor at the University of Twente,

on the authority of the rector magnificus,

prof. dr. H. Brinksma,

on account of the decision of the graduation committee,

to be publicly defended

on Wednesday, 3 November 2010 at 15:00hrs

by

Rameswor Shrestha Born on 25 November 1976 in Nepal This dissertation is approved by

the promotor Prof. dr. ir. Bram Nauta and

the assistant promotor Dr. ir. Ronan van der Zee

To my parents,

and my aunts

# **Contents**

| Chapte | r 1 Introduction                                                 | 1  |

|--------|------------------------------------------------------------------|----|

| 1.1    | Brief History of Radio                                           | 1  |

| 1.2    | Spectrum Scarcity and Usage                                      | 2  |

|        | 1.2.1 Spectral efficiency enhancement trends                     | 3  |

|        | 1.2.2 Spectrum sharing trends                                    | 5  |

| 1.3    | Software-Defined Radio Transmitters                              | 5  |

| 1.4    | Scope of this thesis                                             | 6  |

| 1.5    | Outline                                                          | 7  |

| Chapte | r 2 Linearity, Efficiency and Flexibility of RF Power Amplifiers | 9  |

| 2.1    | Digitally Modulated Signal Characteristic                        | 10 |

| 2.2    | Measuring Linearity and Efficiency of Power Amplifiers           | 15 |

|        | 2.2.1 Measuring linearity                                        | 15 |

|        | 2.2.2 Efficiency measurement                                     | 18 |

| 2.3    | Basic Linear and Switch Mode Power Amplifiers                    | 20 |

|        | 2.3.1 Linear mode Power Amplifiers                               | 20 |

|        | 2.3.2 Switched Mode Power Amplifiers                             | 23 |

| 2.4    | Efficiency Enhancement Techniques                                | 25 |

|        | 2.4.1 Doherty Amplifier                                          | 25 |

|        | 2.4.2 Outphasing Amplifier                                       | 29 |

|        | 2.4.3 Adaptive Bias                                              | 32 |

|        | 2.4.4 Envelope Elimination and Restoration or Polar Modulation   | 32 |

|        | 2.4.5 Envelope Tracking                                          | 33 |

|        | 2.4.6 Summary of Efficiency Boosting Techniques                  | 34 |

| 2.5    | Output Filtering                                                 | 34 |

| 2.6    | Summary and Conclusions                                          | 35 |

| Cł | ıapteı | r 3 Wio  | deband Power Upconverter for Software Defined Radios | 39 |

|----|--------|----------|------------------------------------------------------|----|

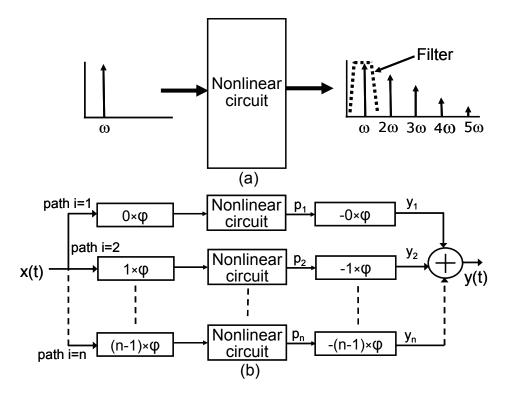

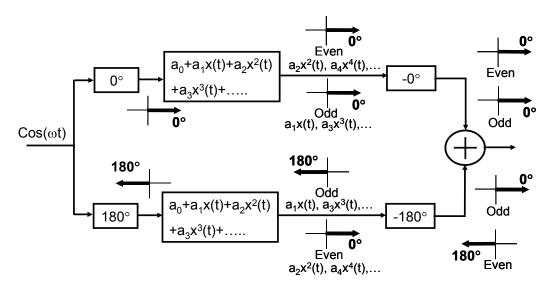

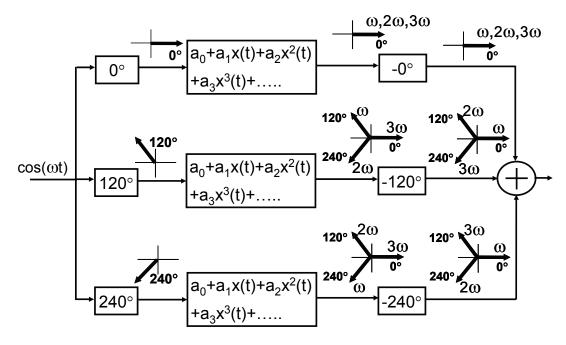

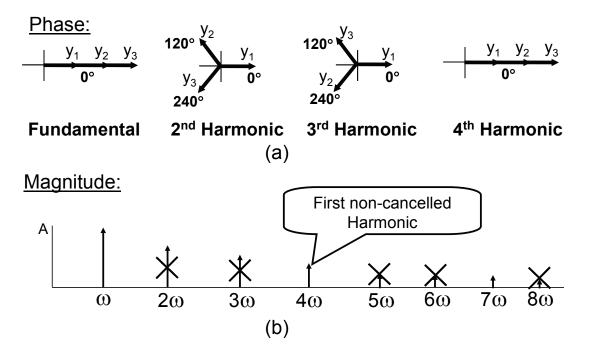

|    | 3.1    | Polyp    | hase Multipath Technique                             | 40 |

|    |        | 3.1.1    | Basic Principle of Harmonic Cancellation             | 40 |

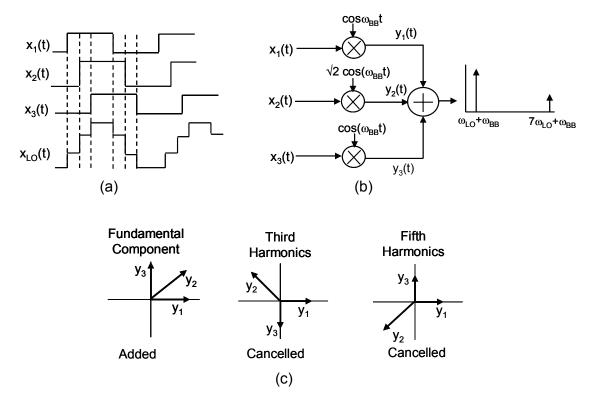

|    |        | 3.1.2    | Polyphase 2-path and 3-path circuit examples         | 42 |

|    |        | 3.1.3    | Generalization to intermodulation distortion         | 45 |

|    |        | 3.1.4    | Conclusion                                           | 45 |

|    |        | 3.1.5    | Discussion                                           | 45 |

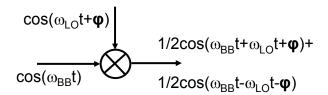

|    | 3.2    | Mixer    | as a phase shifter and frequency shifter             | 46 |

|    | 3.3    | Filter-  | less Power Upconverter Design                        | 49 |

|    |        | 3.3.1    | Basic Power Upconverter                              | 49 |

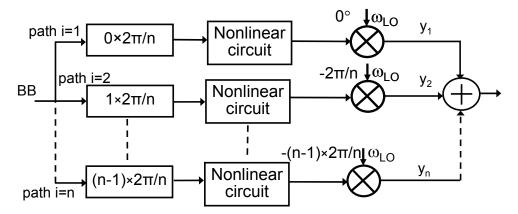

|    |        | 3.3.2    | n-path Power Upconverter                             | 50 |

|    | 3.4    | Circui   | t Implementation                                     | 54 |

|    |        | 3.4.1    | Overview                                             | 54 |

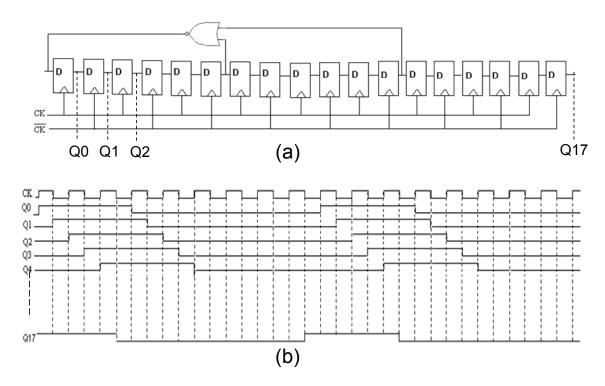

|    |        | 3.4.2    | Multiphase Signal Generation Circuit                 | 54 |

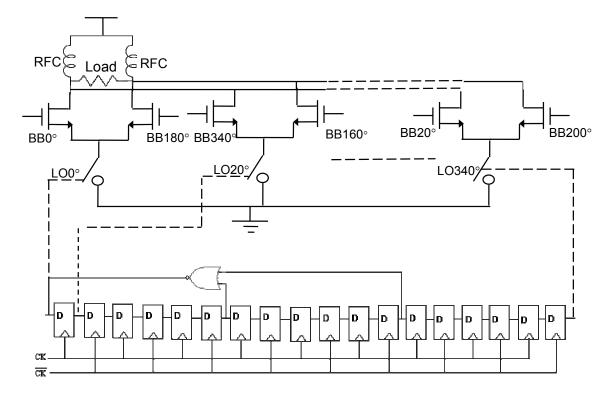

|    |        | 3.4.3    | Power Upconverter Circuit                            | 56 |

|    |        | 3.4.4    | Mismatch                                             | 57 |

|    | 3.5    | Exper    | imental Results                                      | 58 |

|    | 3.6    | Concl    | usion                                                | 63 |

| Cł | ıapteı | r 4 Pola | ar Modulated Power Amplifiers                        | 65 |

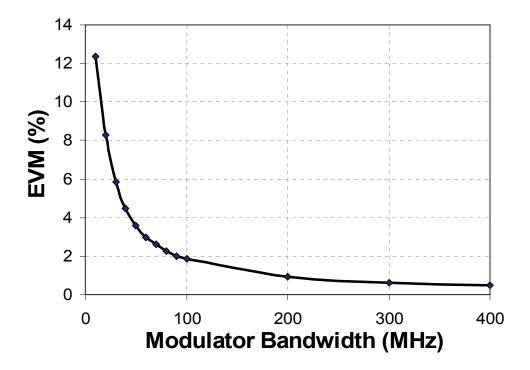

|    | 4.1    | Challe   | enges of Polar Modulated Power Amplifiers            | 66 |

|    |        | 4.1.1    | Bandwidth of Supply Modulator                        | 66 |

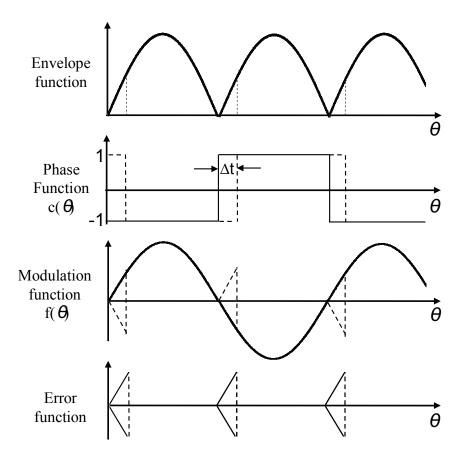

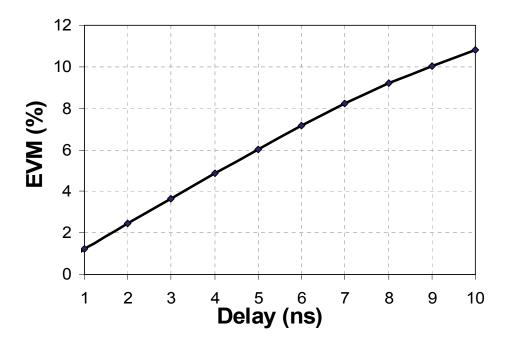

|    |        | 4.1.2    | Differential delay between envelope and phase paths  | 67 |

|    |        | 4.1.3    | Switching Noise of the Supply Modulator              | 69 |

|    |        | 4.1.4    | Feed-through                                         | 69 |

|    |        | 4.1.5    | Nonlinear Parasitic Output Capacitance               | 73 |

|    |        | 4.1.6    | Conclusion                                           | 75 |

|    | 4.2    | Suppl    | y Modulator Design                                   | 75 |

|    |        |          |                                                      |    |

|           | 4.2.1    | Overview of Operation                             | 75  |

|-----------|----------|---------------------------------------------------|-----|

|           | 4.2.2    | IEEE 802.11g WLAN Signal                          | 77  |

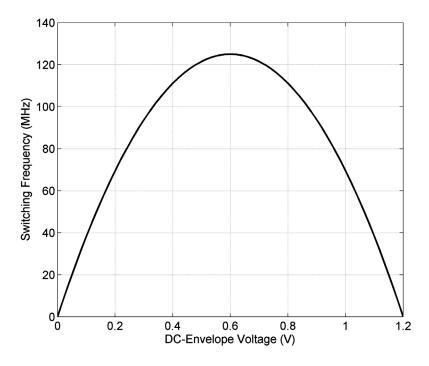

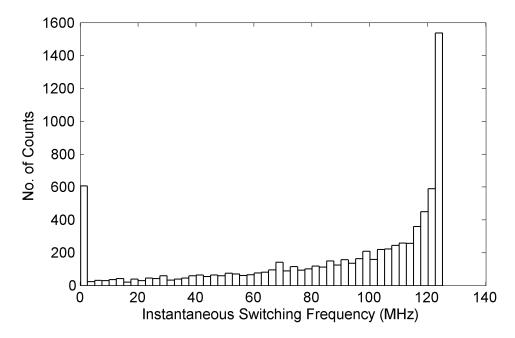

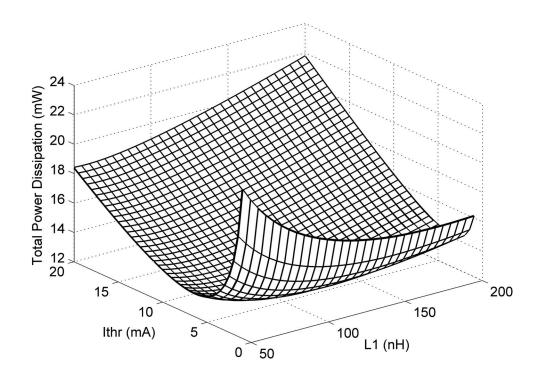

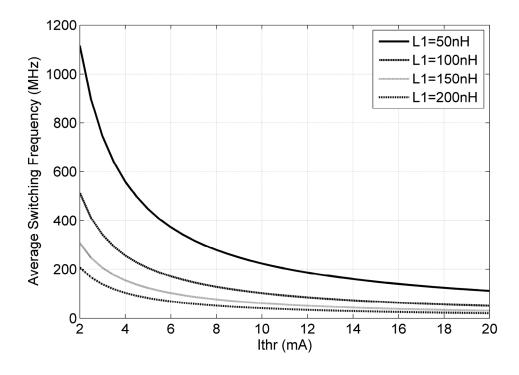

|           | 4.2.3    | Switching Frequency                               | 79  |

|           | 4.2.4    | Dissipation                                       | 81  |

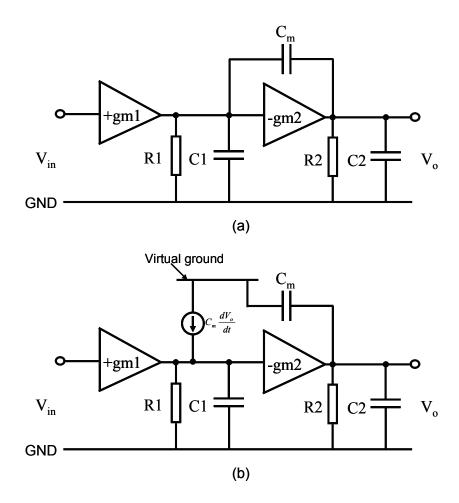

|           | 4.2.5    | First Order Model for Efficiency Optimization     | 81  |

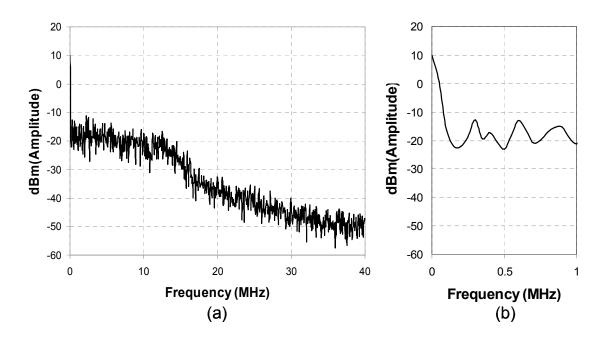

|           | 4.2.6    | Switching Residue                                 | 85  |

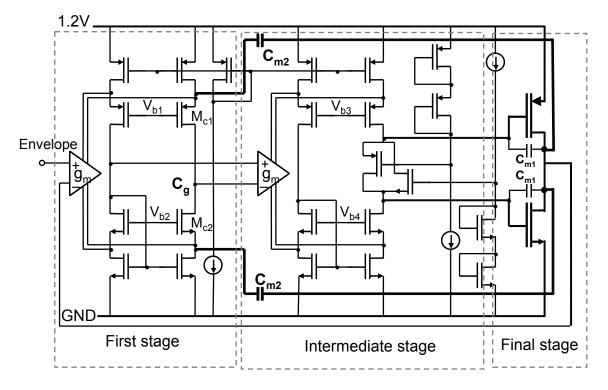

| 4.3       | Circui   | it Implementation of a Supply Modulator           | 86  |

|           | 4.3.1    | Class AB amplifier                                | 86  |

|           | 4.3.2    | Class D amplifier                                 | 90  |

|           | 4.3.3    | Sense and control circuit                         | 91  |

| 4.4       | Circui   | it Implementation of a Class-E RF Power Amplifier | 92  |

| 4.5       | Meası    | urements                                          | 100 |

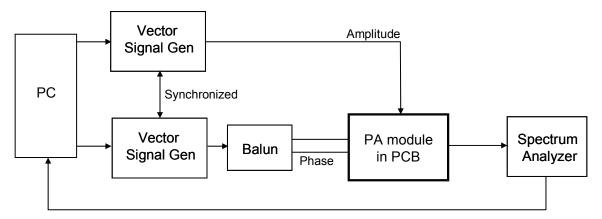

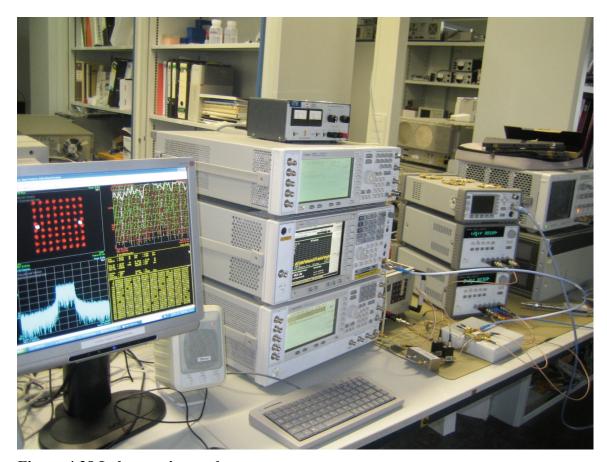

|           | 4.5.1    | Polar Modulated Power Amplifier Module Prototype  | 100 |

|           | 4.5.2    | Measurement Setup                                 | 102 |

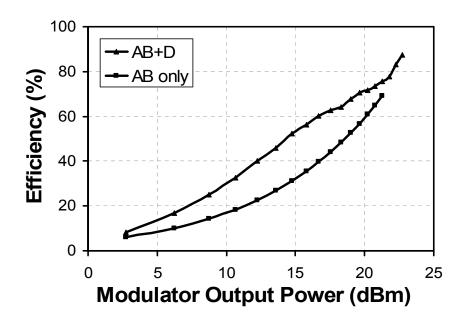

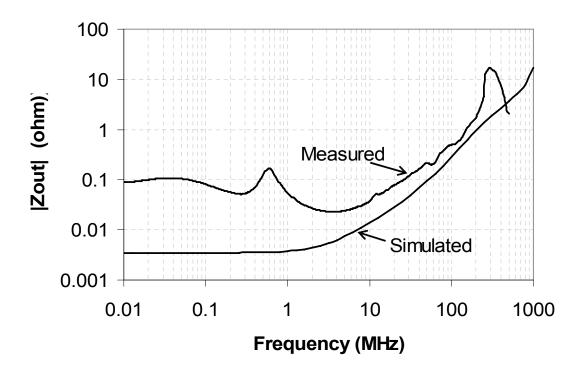

|           | 4.5.3    | Measurement Results                               | 103 |

| 4.6       | Concl    | usions                                            | 107 |

| Chantei   | r 5 Cor  | aclusions                                         | 111 |

| 5.1       |          | nary and Conclusions                              |     |

|           |          | nal Contributions                                 |     |

| 5.3       |          | nmendations for Future Work                       |     |

| Samenv    | atting . |                                                   | 115 |

| Append    | ix A C   | anceling Harmonics with 3-paths                   | 117 |

| List of I | Publica  | tions                                             | 119 |

| Acknow    | ledgen   | 1ents                                             | 121 |

| About t   | he Autl  | hor                                               | 123 |

# **Chapter 1**

#### Introduction

# 1.1 Brief History of Radio

The era of wireless communication began when Heinrich Hertz proved the Maxwell's theory of electromagnetism that predicted the existence of electromagnetic waves. In 1887, Hertz demonstrated the transmission and reception of electromagnetic waves as predicted by Maxwell through his experiment. His radio transmitter system consisted of a high voltage induction coil, a condenser and two brass conductors separated by a tiny gap to cause a spark discharge. Once a spark was generated, a conducting path was formed between the spark-gap and the charge could rapidly oscillate back and fourth at a frequency determined by the values of the capacitor and the induction coil. The receiver was a loop made from copper wire with a small gap in the loop. When the spark-gap transmitter generated a spark, a small spark was seen to jump the gap in the receiving coil. He could detect the radio waves few meters from the transmitter in his lab.

At that time Hertz thought his work has no practical application [1], and it was Guglielmo Marconi who used radio waves for communication and commercialized a practical system. Using an improved spark-gap transmitter, coherer-receiver and other various inventions at that time, he was able to transmit radio signals for about a mile at the end of 1895. In 1897, he established world's first radio station in England. In the same year, he formed his first company "Wireless Telegraph and Signal Company" in Britain. Marconi basically assembled inventions from Nikola Tesla, Oliver Lodge, Edouard Branly, etc., and used them to improve his radio system. Entrepreneur Marconi's company was able to transmit first trans-Atlantic radio signal in 1901, although the claim is later disputed [2]. He established the first permanent transatlantic wireless services from Clifden, Ireland to Glace Bay, Nova Scotia, Canada in 1907.

The importance and usefulness of wireless communication was further highlighted following the sinking of the RMS Titanic in 1912, including communications between

operators on the sinking ship and nearby vessels, and communications to shore stations listing the survivors [3]. Distress signal using wireless telegraphy from the Titanic made a great impression on the public regarding the usefulness of wireless communications.

The invention of the triode vacuum tubes by Lee De Forest in 1907 was a great step forward toward better transmitters and receivers. One terminal of the triode, called grid, controlled the current and made amplification possible. This allowed for amplitude modulation of a continuous wave signal and made voice transmission practical. Transmission with continuous wave signal is narrowband whereas spark-gap transmitters emitted wideband signals causing a serious interference problem. With an improved triode, the transmitters were made more power efficient. In 1921, the Detroit police experimented with one way voice transmission to cars. Two-way police radio, with the equipment occupying most of the car trunk, began in mid 1930s.

World War II resulted in the mass production of radio equipment in order to equip the increasing number of aircrafts and ships. The widespread use of wireless communication using telegraph, broadcasting, telephones, and point to point radio links, was accelerated during and after the war.

The invention of the transistor, drastically reducing the size and power consumption of the radio system, started a new era in electronics. By 1966, the first pocket-sized mobile phones were produced. After 1980, cellular phones and cordless phones became very popular and enjoyed very rapid growth till date.

Today, developments in radio technology are as exciting as Marconi's first transatlantic wireless communication. Recently, the International Telecommunication Union (ITU) predicted that the number of mobile cellular subscribers worldwide will reach the 5 billion mark by the end of 2010. This is an astonishing number, comparing with the world population of 6.87 billion. Another exciting example of the use of radio waves is in the space exploration. For example, NASA collects observations from the twin Voyager I and II spacecraft, which are over 12 billions kilometers away from the earth and at the edge of our solar system. It takes over 14 hours for the signal to reach the earth from the Voyager I.

## 1.2 Spectrum Scarcity and Usage

Early wireless telegraph communication had a moderate messaging rate of about 25 words per minute using Morse code signaling. This is equivalent to about 20bps of data rate. So the information bandwidth was just 10s of Hertz where as spark-gap transmitter emitted 100s of kHz wideband band signals. Spectral efficiency was very poor and interference was a serious problem. After the establishment of world's first spectrum regulatory body in 1934, the Federal Communications Commission (FCC) in the United States, radio transmissions needed to be licensed and separated in frequency, and were not allowed to cause interference to other users. Since its establishment, it assigns users to specific frequencies. These include AM, FM, short wave and citizen bands and VHF and UHF television channel, radio amateurs, cellular and cordless telephones, air traffic

control radars, security alarms, radio controlled toys etc. Demand for spectrum continues to grow.

The FCC frequency allocation chart [4] now shows a heavily crowded spectrum with virtually all usable radio frequency bands already licensed to commercial operators and government entities for specific services, making spectrum a scarce resource. Two different trends for the *optimal spectrum utilization* are discussed in this section.

#### 1.2.1 Spectral efficiency enhancement trends

Spectrum bandwidth can be very expensive, at least in some mobile communication scenarios. For example, Vodafone paid \$9 billion to acquire a license for UMTS operation for 2×15MHz bandwidth in the United Kingdom through auctions [5]. On the other hand, the demand for high data rates is increasing rapidly for wireless communications. So modern radio transmission and networking technologies should offer very high data rates within a limited available bandwidth, and thus increase the spectral efficiency.

A straight forward way to provide higher data rates within a given bandwidth is the use of higher-order modulation, thereby allowing more bits of information to be encoded per modulation symbol. For example in case of Quadrature Phase Shift Keying (QPSK) modulation scheme, the modulation alphabet consists of four different signaling alternatives. So QPSK allows for 2 bits of information to be communicated in each symbol. Similarly, 16QAM (Quadrature Amplitude Modulation) modulation scheme has sixteen different signaling alternatives. Thus it allows 4 bits of information to be encoded in each symbol. 64QAM modulation scheme allows 6 bits of information to be communicated in each symbol. So theoretically the spectral efficiency (bits/s/Hz) of 16QAM and 64QAM modulation is two and three times that of QPSK respectively. However the process of concentrating more and more bits per symbol cannot go on without limit. While the bandwidth utilization goes up, higher order modulation schemes such as 16QAM and 64QAM require a higher signal-to-noise ratio at the receiver for a given bit error rate (BER) compared to QPSK.

Another way to increase the data rates, without suffering from increased signal corruption is to increase the overall transmission bandwidth by means of multiple-carrier transmission. In multi-carrier transmission, many narrowband signals often called subcarriers, which are modulated by different data stream, are frequency multiplexed and jointly transmitted over the same radio link to the same receiver. By using N-sub-carriers, the overall data rate is increased by N times. One special case of multi-carrier transmission is Orthogonal Frequency Division Multiplexing (OFDM) transmission. It utilizes the available bandwidth efficiently by employing a number of closely spaced orthogonal carrier frequencies with a total symbol rate near the Nyquist rate. Generally OFDM has a nearly 'white spectrum'. Modern wireless communication standards increasingly use more and more complex modulation schemes and multiple carriers in order to increase spectral efficiency.

A general drawback of higher order modulation scheme and multi-carrier evolution is the large peaks in the instantaneous signal power. With the higher order modulation scheme such as 16QAM and 64QAM, the information is encoded in the instantaneous amplitude as well as phase of the modulated signal. As a result, the modulated signal will have large variations in the instantaneous power, thus the larger peaks. Probability of the larger peaks in the instantaneous power is higher for high order modulation [6] at a given average power. The ratio of the peak power to the average power of the signal which is called Peak to Average Power Ratio (PAPR) is higher for 64QAM than for QPSK modulated signal. Similarly the parallel transmission of multiple carriers will also lead to a larger variation in instantaneous transmitted power and thus to a higher peak to average power ratio. Table 1.1 shows the modulation format, PAPR, peak data rate and channel bandwidth for a number of widely used standards. The PAPR can be as high as 10dB in the case of WLAN signals.

| Standards              | Modulation Format                      | Operating<br>Frequency                               | PAPR                                                           | Peak Data<br>Rate                | Channel<br>Bandwidth |

|------------------------|----------------------------------------|------------------------------------------------------|----------------------------------------------------------------|----------------------------------|----------------------|

| GSM<br>(2G)            | GMSK                                   | 900MHz, 1800MHz,<br>1900MHz                          | 0dB                                                            | 22.8kbps<br>(9.6kbps<br>nominal) | 200kHz               |

| GSM EDGE<br>(2.5G)     | 8-PSK                                  | 900MHz,1800MHz,<br>1900MHz                           | 3.2dB                                                          | 59.2kbps/time<br>slot            | 200kHz               |

| WCDMA/UM<br>TS (3G)    | QPSK (downlink)<br>OCQPSK (uplink)     | 1920-1980 MHz<br>2110-2170 MHz                       | 3.5-7dB                                                        | 2Mbps                            | 5MHz                 |

| CDMA2000<br>(3G)       | QPSK/BPSK/8-PSK<br>/16QAM (adaptive)   | 450, 700, 800, 900,<br>1700, 1800, 1900,<br>2100 MHz | 4-9dB                                                          | 3.1Mbps                          | 1.25MHz              |

| IEEE 802.11b<br>(WLAN) | DBPSK,<br>DQPSK,CCK                    | 2.4GHz (ISM)                                         | As high as 10dB<br>(10log <sub>10</sub> (N) dB,<br>N=carriers) | 11Mbps                           | 20MHz                |

| IEEE 802.11g<br>(WLAN) | BPSK,QPSK, 16-<br>QAM, 64-<br>QAM,OFDM | 2.4GHz (ISM)                                         | As high as 10dB<br>(10log <sub>10</sub> (N) dB,<br>N=carriers) | 54Mbps                           | 20MHz                |

| IEEE 802.11a<br>(WLAN) | BPSK,QPSK, 16-<br>QAM, 64-<br>QAM,OFDM | 5.1-5.8GHz                                           | As high as 10dB<br>(10log <sub>10</sub> (N) dB,<br>N=carriers) | 54Mbps                           | 20MHz                |

Table 1.1: Modern standards demanding a high peak to average power ratio (PAPR)

Amplifying signals with a large peak to average power ratio using a conventional linear Power Amplifier (PA) can satisfy the linearity requirement but suffers from poor efficiency because these power amplifiers inherently operate far below their saturated output power level where the efficiency is maximum. High power efficiency is especially important for portable devices due to the desire for longer battery life. So for such applications modern power amplifiers should overcome the traditional linearity-efficiency trade-offs.

#### 1.2.2 Spectrum sharing trends

As mentioned earlier, most of the spectrum (below 5GHz) for wireless communication is densely allocated by regulatory bodies, making bandwidth a scarce resource. As the demand for RF spectrum continues to grow, it is unlikely that the bandwidth requirement of new technologies can be met. As a result spectrum access can slow down the development of emerging radio services that can greatly improve our life style, health, safety, education of people, and work environment. However, on the other hand studies suggest that the spectrum bandwidth of most wireless communication systems is not utilized for a significant amount of time at a given location [7]. For example, the spectrum for commercial mobile communications is used heavily. But the spectrum utilization for amateur radio is poor. So, spectrum scarcity is in fact due to the inefficiency of the fixed frequency allocation pursued by our radio regulators. As an example, the situation can be compared with a busy highway where one lane is allocated for ambulance; another lane is allocated for fire-fighting vehicle and so on. The lanes for the ambulance and the fire-fighting vehicle are rarely used and most of the time free where as remaining lane is heavily used, often with traffic problems.

In order to overcome this problem, dynamic spectrum access with cognitive radio technologies, which is now one of the developments taking place, can be a revolutionary approach to increase the efficiency of spectrum usage as it redefines the traditional frequency allocation approach. It allows unlicensed wireless users (secondary users) to operate in the licensed bands from legacy spectrum holders (primary users) on a negotiated or an opportunistic basis without harmful interference or disturbance to the communications of the primary users. By actively monitoring the radio frequency environment, radio terminals dynamically select empty frequency spectrum and change transmission and reception parameters like power, frequency, modulation etc accordingly. Engineers and scientist around the world are now working to bring that kind of flexible, adaptive and reconfigurable system with operating intelligence to future radios. The idea of cognitive radio was described by Joseph Mitola in [8]. As current demand for spectrum looking to increase, some regulatory bodies like FCC in the USA and Ofcom in the United Kingdom are looking favorably at the idea of cognitive radio. It has the potential to alleviate the spectrum scarcity.

In addition to the high level of processing required for the cognitive radio realization, a hardware platform is needed to be particularly flexible, allowing for flexible choice of the radio frequency depending on free available spectrum. Traditional hardware can not handle this requirement because they are band limited, optimized primarily for low cost and low power, and not flexible.

## 1.3 Software-Defined Radio Transmitters

In recent years, the explosive growth in the wireless market has led to wireless transceiver terminals that have multiple applications and cover multiple standards. Nowadays, it is not uncommon to have tri- or quad-band GSM, WCDMA, IEEE 802.11a/b/g wireless LAN, Bluetooth, and GPS in the same phone. Much more

functionalities are expected to be added in the future. The current approach of multistandard radio is to use multiple transceivers with their own RF and baseband circuitry, one for each standard.

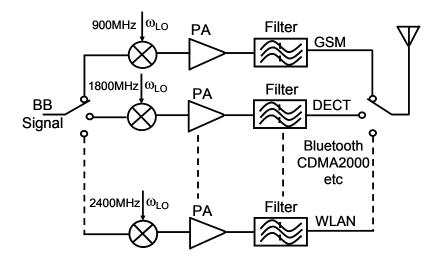

Figure 1.1: Conventional multi-standard transmitter architecture

Fig. 1.1 shows a typical example of a multi-standard transmitter, with multiple narrow-band power amplifiers which are limited in bandwidth mainly by *dedicated filters*, one for each standard, selectable by a switch. With the ever increasing number of different standards to be supported, this architecture becomes increasingly unpractical, as support for every new frequency band requires adding external dedicated components and more die area. A dream is to have a much more flexible radio, which can support many different standards. If you insist on a visionary view: we aim for "the holy grail of software radio". A software defined radio is the radio in which some or all of the physical layer functions are software-defined [9]. Cognitive radio can also be viewed as an extension of a software-defined radio. So as in the case of cognitive radio, a software-defined radio needs a flexible or reconfigurable hardware platform to allow for a flexible choice of the radio frequency. One of the main obstacles in implementing a flexible or reconfigurable transmitter is the fixed frequency output filter, needed to suppress the strong harmonics generated by the power amplifier to acceptable levels.

## 1.4 Scope of this thesis

In section 1.2 and 1.3, we discussed two separate problems in modern wireless communication systems that are mainly related to the power amplifiers for the radio front-end; (a) a transmitter power efficiency problem amplifying signals with a large PAPR and (b) a lack of flexible RF front-ends to choose an arbitrary RF transmitter frequency. In this thesis, we separately cover solutions to these two different problems. The scope is limited to the RF front-end of the transmitter.

#### 1.5 Outline

In chapter 2, the properties of a complex digital modulated signal and different methods to measure the linearity and efficiency of power amplifiers is discussed. This chapter also presents the basic power amplifiers classes and efficiency enhancement techniques. Similarly, different ways to obtain a flexible RF transmitter front-end with the focus on the power amplifier and RF output filter are explained.

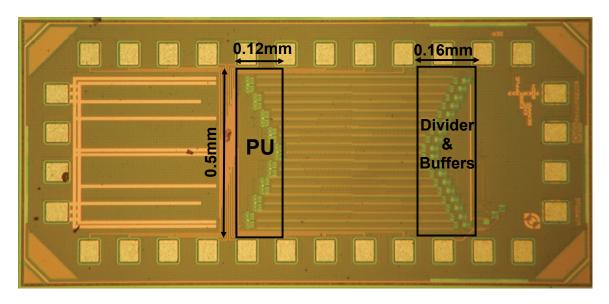

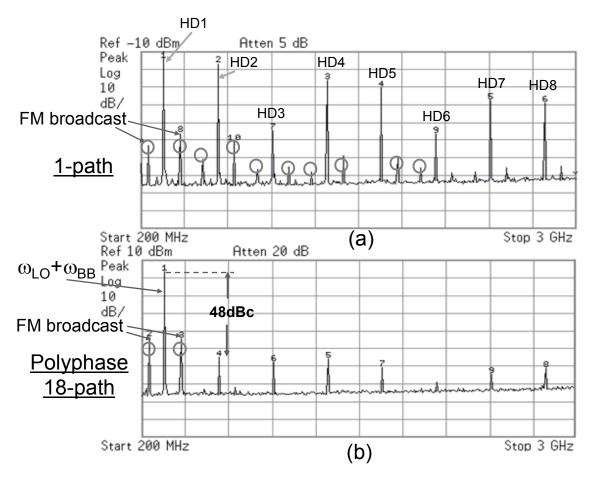

In chapter 3, a detailed analysis of the polyphase multipath circuit technique is presented. The technique is applied to realize a wideband *filter-less* power upconverter by canceling a very large multitude of harmonics and sidebands. The design is realized in a 0.13µm CMOS process which mainly focuses on a proof-of-concept of the polyphase multipath technique. This chapter also presents measurement results of the demonstrator chip.

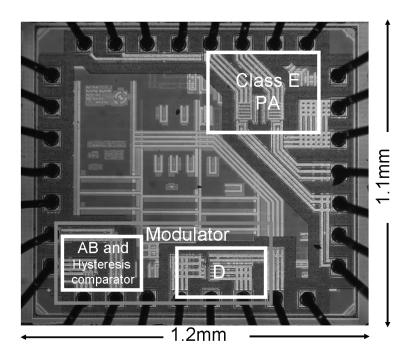

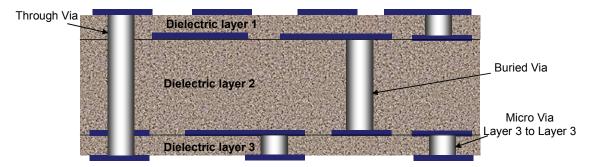

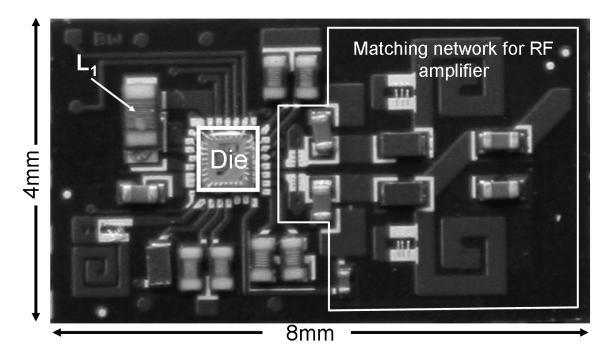

In chapter 4, the design of a polar modulated power amplifier, which is one of the efficiency enhancement techniques, is presented. First, the main challenges in implementing a polar modulated PA are explained. Then, the overview of the system to overcome those challenges is given. This chapter also discusses the design of the supply modulator, one of the tough building blocks in a polar modulated PA. Finally, the measurement results of the prototype chip fabricated in a 65nm CMOS with the off-chip passive components on a laminate module is presented in this chapter.

Chapter 5 offers conclusions and presents suggestions for future work.

#### References

- [1] G.R.M. Garratt, "The early history of radio: from Faraday to Marconi", London, Institution of Electrical Engineers in association with the Science Museum, History of technology series, 1994

- [2] J.S. Belrose, "Fessenden and Marconi: Their Differing Technologies and Transatlantic Experiments during the First Decade of this Century", *International Conference on 100 Years of Radio*, 5-7 September 1995

- [3] T. H. White, "United States Early Radio History" (online): http://earlyradiohistory.us

- [4] NTIA, "FCC Frequency Allocation Chart", 2003; (online): http://www.ntia.doc.gov/osmhome/ allochrt.pdf

- [5] K. Binmore and P. Klemperer "The Biggest Auction Ever: the Sale of the British 3G Telecom Licences", *Economic Journal*, pp 74-95, March 2002

- [6] E. Dahlman, S. Parkvall, J. Sk"old, and P. Beming, "3G Evolution: HSPA and LTE for Mobile Broadband", Academic Press, Oxford, UK, 2007

- [7] FCC Spectrum Policy Task Force, "Report of the spectrum efficiency working group", (Online): http://www.fcc.gov/sptf/reports.html, Nov. 2002

- [8] J. Mitola, "Cognitive Radio: An Integrated Agent Architecture for Software Defined Radio" Ph.D. dissertation, KTH, Stockholm, Sweden, December 2000

- [9] SDR Forum, "SDRF Cognitive Radio Definitions", (online): http://www.sdrforum.org/pages/documentLibrary/documents/SDRF-06-R-0011-V1\_0\_0.pdf

# Chapter 2

# Linearity, Efficiency and Flexibility of RF Power Amplifiers

The Power Amplifier is often one of the most power consuming building blocks in a portable device. It is also the last building block that determines the quality of the transmitted signal. So, on one hand a power amplifier has to be efficient to increase the talk time or the battery life time and on the other hand the transmitted signal should satisfy the linearity requirements.

The type of modulation used in a particular standard has a great impact on the design of a power amplifier. First generation analog cellular systems like the Advanced Mobile Phone System (AMPS), the European Total Access Communication system (ETACS), and the Japanese Access Communication system (TACS) use a frequency modulation scheme, which results in a constant amplitude signal [1], [2]. Similarly the Global System for Mobile Communication (GSM), the most widely accepted second generation digital cellular standard, uses a Gaussian Minimum-shift Keying (GMSK) digital modulation scheme. GMSK is a special type of phase modulation and also results in a constant amplitude signal. Since those standards use a modulation scheme that results in a constant amplitude signal, a non-linear amplifier which has a high efficiency can be used to amplify those signals. As a result, traditional power amplifier design often ignores the characteristics of the signal. Designers rather focus on optimizing the efficiency at the saturated output power by playing with the device technology and the circuit design. However, as the demand for high data rate increases rapidly, modern wireless standards are forced to use spectrally efficient complex modulation schemes and multiple carriers that contain information both in amplitude and phase. Such signals have a variable envelope with high peak-to-average power ratio. To design a power amplifier for such systems, the understanding of the characteristics of the modulated signal is necessary to optimize the power amplifiers performance in terms of both linearity and efficiency. Section 2.1 discusses different digital modulation scheme and the signal characteristic from the power amplifier prospective. Different ways to measure the linearity of power amplifiers used to amplify complex digital signal is presented in section 2.2. In section 2.3, basic (classic) linear and switch mode RF power amplifiers are discussed. These amplifiers always have a trade-off between linearity and efficiency. Efficiency enhancement techniques that defy the traditional linearity/efficiency trade-off are explained in section 2.4. Section 2.5, finally, deals with the output filtering challenges for software defined radio and cognitive radio.

# 2.1 Digitally Modulated Signal Characteristic

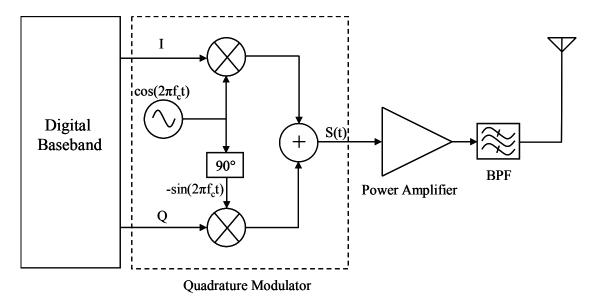

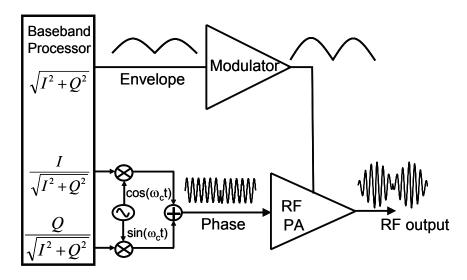

In digital modulation, a digital data stream is modulated with an analog carrier signal. Figure 2.1 shows a typical transmitter architecture used in a digital wireless communication system. A digital baseband processor generates an in-phase (I) and a quadrature phase (Q) component from the stream of bits that need to be transmitted. The baseband signal is then frequency up-converted to RF by using a quadrature modulator. In the quadrature modulator, I and Q signals are modulated with the in-phase and the quadrature-phase carriers respectively. The outputs are then summed up to yield the modulated signal:

$$S(t) = I\cos(2\pi f_c t) - Q\sin(2\pi f_c t) \tag{2.1}$$

where  $f_c$  is the carrier frequency.

The modulated bandpass RF signal of equation (2.1) can also be represented in polar form by:

$$S(t) = A(t)\cos(2\pi f_c t + \varphi(t))$$

(2.2)

Where

$$A(t) = \sqrt{I^2 + Q^2}$$

and  $\varphi(t) = \tan^{-1} \left(\frac{Q}{I}\right)$

The modulated RF signal is then amplified by a power amplifier before it is fed to antenna.

Figure 2.1: Typical linear transmitter architecture

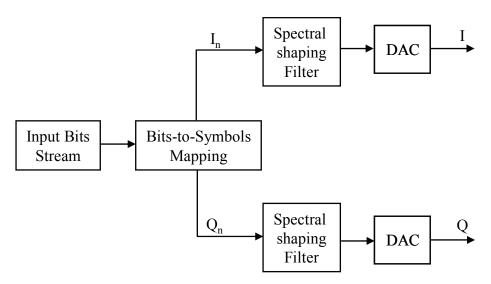

Figure 2.2: A typical block diagram of a digital baseband

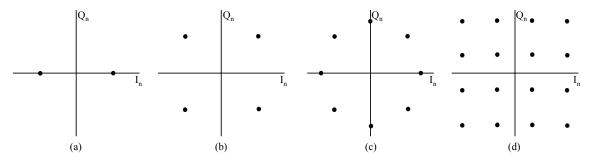

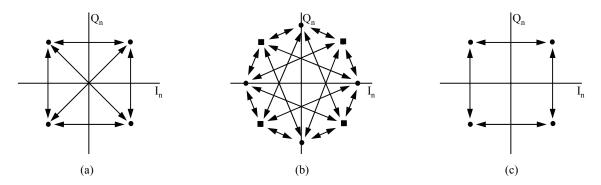

In a digital baseband circuitry as shown in Figure 2.2, incoming bits stream are mapped into unique symbols that contains an in-phase  $(I_n)$  and a quadrature-phase  $(Q_n)$  component. Symbols are vectors. It can be represented in an IQ-plane. The placement of symbol constellation points in the IQ-plane is based on the modulation format, a pattern used to map the incoming bits. Figure 2.3 shows constellations pattern in the IQ-plane for various modulation formats. One or more bits can be encoded in each symbol, depending on the modulation format. Some common types of digital modulation format are:

i) Phase Shift keying (PSK): In PSK modulation, the phase of a carrier signal is varied to represent the information to be sent. As a result, constellation points in the IQ plane are distributed on the unit circle. One of the simplest forms of this kind of modulation is a

binary phase shift keying (BPSK) where the phase of a carrier signal changes between 0° and 180°. In an IQ diagram of BPSK, the I state has two different values to represent a binary '1' and '0' as shown in Figure 2.3(a). One of the most commonly used phase modulation scheme such as in CDMA2000 and Digital Video Broadcasting-Satellite (DVB-S) standards is a Quadrature Phase Shift Keying (QPSK). QPSK has four states: two I values and two Q values as shown in Figure 2.3(c), thus giving 2 bits per symbol. Similarly 8-PSK modulation has 8 states and modulates 3 bits per symbol.

Figure 2.3: Constellation pattern in the IQ plane for a) BPSK, b) QPSK, c) 8-PSK and  $\pi/4$ -shifted-QPSK, d) 16QAM

**Filtering:** A signal with step change in phase or amplitude requires a large bandwidth. So filtering is required to transmit the digital information in the smallest possible bandwidth without introducing inter-symbol interference (ISI). The shape and bandwidth of the I and Q signal, and hence the actual signal trajectories, depend on the characteristics of the filter. Some common types of pulse shaping filters [3] are:

- Root Raised Cosine

- Half-Sinusoid

- Gaussian

**Signal Trajectory:** The trajectory of the transition between the states in the symbol defines some important characteristics of the modulated signal S(t). Figure 2.4(a) shows the signal transitions for QPSK modulation before filtering. From the power amplifier prospective, two things are clear from this figure. The first one is that some of the transition of states, sketched as straight line, travel through zero (origin), thus causing the amplitude of the modulated signal to also cross zero. A zero crossing can create problem in power amplifier design as it needs infinite dynamic range. The second is that the modulated signal has varying envelope as it moves to different states. So a linear amplifier is required to amplify such signal.

A special type of QPSK modulation called  $\pi/4$ -shifted-QPSK is proposed to avoid zero crossing of the modulated carrier signal amplitude. The signal constellation of  $\pi/4$ -shifted-QPSK can be viewed as a superposition of two QPSK constellations offset by  $\pi/4$  relative to each other as shown in Figure 2.4(b). Symbol phases are changed from one of the QPSK constellations to the other alternatively, meaning that a QPSK constellation is shifted by  $\pi/4$  radians in every alternate symbol. So a relative phase transition between states in successive symbols is either  $\pm \pi/4$  radian or  $\pm 3\pi/4$  radian. This avoids the

transitions in the signal constellation to pass through origin. As a result the envelope of  $\pi/4$ -shifted-QPSK exhibits less variation than that of QPSK, making the signal more power amplifier friendly. There is also a differential version of  $\pi/4$ -shifted-QPSK called  $\pi/4$ -shifted-DQPSK (differential quadrature phase-shift keying) modulation in which the information is encoded in the magnitude and direction of the phase shift, not in the absolute position of the constellations. The  $\pi/4$ -shifted-DQPSK modulation format is used in NADC-IS-54 (North American Digital Cellular), PHS (Personal Handyphone System), TETRA (Trans European Trunked Radio), PDC (Personal Digital Cellular) and others.

Figure 2.4: Signal transitions for a) QPSK, b)  $\pi/4$ -shifted-QPSK, c) OQPSK

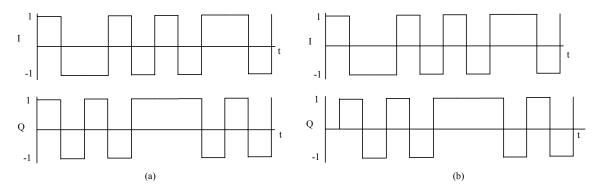

Another important variant of QPSK is offset QPSK (OQPSK). In OQPSK, the Q signal is delayed by half a symbol period as shown in Figure 2.5(b) so that the transition of I and Q channels of the OQPSK do not occur at the same time. In the constellation diagram, signal transitions only occur to neighbors (see Figure 2.4(c)). To go through the phase transition of  $\pi$ , the OQPSK makes two transitions of  $\pi/2$  in each half of the symbol period. Hence the maximum phase transition is  $\pi/2$ , and occurs twice as often, but with half the intensity of the QPSK. Square root-raised cosine pulse shaping is used in OQPSK.

Figure 2.5 I and Q channel mappings of (a) QPSK and (b) OQPSK signal

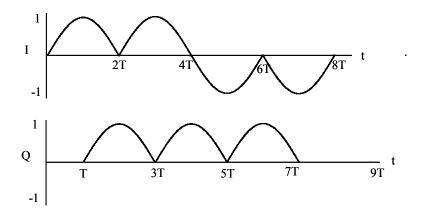

**ii) Minimum Shift Keying (MSK):** MSK is related to OQPSK modulation. The difference is that MSK uses half-sinusoid pulse shaping where as OQPSK uses square root-raised cosine pulse shaping. Figure 2.6 shows MSK pulses. The MSK modulation makes the phase change continuous, with no discrete jump in phase at the symbol edge,

and limited to  $\pm \pi/2$  over a bit period 'T' (half symbol period). As a result the MSK modulated carrier signal has constant envelope and its power spectral density has low side lobes.

Figure 2.6 I and Q component of MSK signal

The phase transition can be made even smother by using a Gaussian pulse shaping filter. This type of modulation is called GMSK (Gaussian Minimum Shift Keying). GMSK modulated carrier signal also has constant amplitude. Highly efficient non-linear amplifier can be used to amplify such constant envelope signal. GMSK is used in GSM.

Note that although MSK and GMSK are conceptually related to OQPSK modulation, they are often classified as FSK (Frequency Shift Keying) modulation owing to the dual nature of phase and frequency modulation [3].

**iii) Quadrature Amplitude Modulation (QAM)**: In quadarature amplitude modulation, the constellation points, typically, lie on a square lattice. As shown in Figure 2.3(d), 16QAM has four I values and four Q values resulting in 16 possible states. The modulation order of QAM can be extended to other variant like 32QAM, 64QAM, and 256QAM, representing each symbol by 5, 6 and 8 bits respectively. The transition can take place from any state to any other state at every symbol time.

Quadrature amplitude modulation is a popular family of digital modulation schemes as it can achieve high spectral efficiency. It is used in applications including Wireless LAN (WLAN), DVB-C (Digital Video Broadcasting-Cable), and Modems. However, as discussed in section I.II, as the modulation order increases, the constellation points are placed closer together and are thus subject to noise and distortion. Highly linear power amplifiers are required to amplify those signals. Unfortunately, as the modulation order increases, the peak-to-average power ratio also increases. This reduces the efficiency of a power amplifier.

# 2.2 Measuring Linearity and Efficiency of Power Amplifiers

The previous section described the characteristic of the digitally modulated signal with respect to the modulation format. The use of spectrally efficiency modulation schemes results in a variable envelope signal. What is important to the power amplifier designer is that the power amplifier used to amplify such signal should be sufficiently linear and efficient. This section discusses several ways to quantify linearity and efficiency of the power amplifier.

#### 2.2.1 Measuring linearity

A power amplifier is essentially a non-linear device as it has to handle a large input/output signal with reasonable power efficiency. Non-linearity in the RF power amplifier creates two main problems: inter-modulation distortion and generation of harmonics. Inter-modulation distortion at the output results in increase bit error-rate or deterioration in EVM and interference to the nearby channels or even violation of the spectral mask. Harmonic distortion, however, in many cases can easily be removed by filtering. The consequence of a filter is that the resulting system is narrowband. Some of the widely used methods to measure the effect of non-linearities on modulated signal are follows:

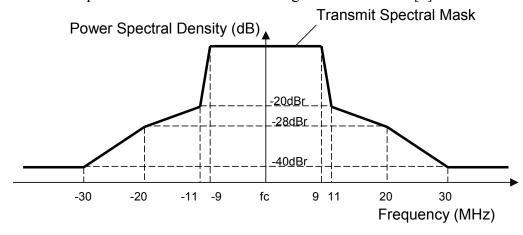

#### 2.2.1.1 Spectral Mask

The spectrum of a transmitted signal should ideally be confined to the assigned frequency band. However, the non-linearity in the transmitter causes the output spectrum to spread in the nearby channels due to the generation of inter-modulation products. Spectral masks are used by standards or regulatory bodies to define the maximum amount of interference that is acceptable. In the assigned band the spectral mask generally has a flat top representing the power level of the transmitted signal and outside the band the mask shows the limits that the transmitter should not exceed. For example Figure 2.7 shows the spectral mask requirement for the IEEE 802.11a/g WLAN standard [4].

Figure 2.7: Spectral mask for the IEEE 802.11a/g WLAN standard

#### 2.2.1.2 Error Vector Magnitude (EVM)

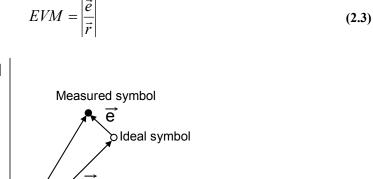

The error Vector Magnitude is the one of the most useful means to quantify the quality of the transmitted or received RF signals, such as digitally modulated signals. Due to various imperfections in the transmitter or receiver chain like non-linearity of the power amplifier, IQ imbalance, gain variations, noise, the constellation points of the transmitted/received signal deviate from their ideal locations. The error vector is a vector in the IQ plane between the ideal constellation point and the point that is measured or received by the receiver. EVM is the magnitude of the error vector, normalized to the signal voltage. As shown in Figure 2.8, EVM is given by,

r e ldeal symbol

Figure 2.8: Error Vector representation

For non-constant amplitude modulation schemes such as QPSK, QAM etc, rms EVM is the root-mean-square power of all error vectors normalized to the reference power. The reference power is the power of the outermost (highest power) symbol, or the average constellation power, or the average reference signal power depending on the particular standard. For IEEE 802.11a/g standard the rms EVM is averaged over subcarriers, OFDM frames and packets, and normalized to the average power of the constellation [4]. The following equation is used to calculate the EVM:

$$Error_{rms} = \frac{\sum_{i=1}^{N_f} \sqrt{\frac{\sum_{j=1}^{L_p} \left[ \sum_{k=1}^{52} \left\{ (I(i,j,k) - I_o(i,j,k))^2 + (Q(i,j,k) - Q_o(i,j,k))^2 \right\} \right]}}{52L_p \times P_0}}{N_f}$$

(2.4)

where

L<sub>p</sub> is the length of the packet;

N<sub>f</sub> is the number of frames

I(i,j,k), Q(i,j,k) denotes the received symbol points of the  $i^{th}$  frame,  $j^{th}$  symbol,  $k^{th}$  subcarrier of the OFDM symbol in the complex plane

$I_0(i,j,k)$ , Q0(i,j,k) denotes the ideal constellation points of the  $i^{th}$  frame,  $j^{th}$  symbol,  $k^{th}$  subcarrier of the OFDM symbol in the complex plane

$P_0$  is the average power of the constellation

Number of subcarriers are 52 (48 data +4 pilot)

The resulting relative constellation RMS error should be smaller than -25dB for 54Mbps data rate (64QAM).

# 2.2.1.3 Adjacent Channel Power Ratio (ACPR) or Adjacent Channel leakage Ratio (ACLR)

Adjacent Channel power Ratio is also a widely used metric to indicate the interference to the adjacent channel caused by the non-linearity of power amplifier.

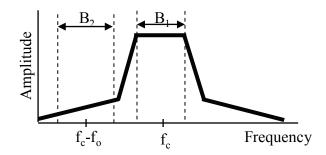

Figure 2.9: ACPR measurement

ACPR is the ratio of the power contained in a defined bandwidth (B<sub>2</sub>) of the adjacent channel at a defined offset (f<sub>o</sub>) from the channel centre frequency (f<sub>c</sub>) to the power in the defined bandwidth (B<sub>1</sub>) of the main signal [5] as shown in Figure 2.9. The bandwidths B<sub>1</sub> and B<sub>2</sub> are not necessarily the same. The ACPR test quantifies the energy of a digitally modulated RF signal that spills from the intended communication channel to the adjacent channel. For many of the current and future transmission standards including CDMA, WCDMA, NADC uses ACPR to characterize distortion generated by the nonlinearity of transmitter circuits. Since power amplifier is the most nonlinear block in the transmitter chain, many power amplifier test systems require measuring this quantity.

#### 2.2.1.4 Noise Power Ratio (NPR)

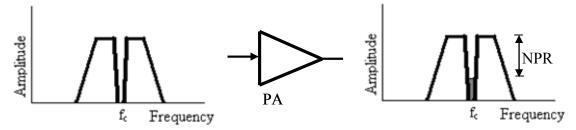

Noise power ratio is the measure of in-channel distortion power caused by the non-linearity of amplifiers. The NPR measurement is an effective way of testing the linearity performance of amplifiers operating with many carriers (>10). For the NPR measurement, white noise is first passed through a bandpass filter to produce an approximately square pedestal of noise. The width of the noise pedestal is usually made equal to the bandwidth of the channel under test. Then this signal is passed through a notch filter to get the noise

pedestal with a deep notch, typically >50dB, as shown in Figure 2.10. This noise signal is used to excite the test PA.

Figure 2.10: Noise power ratio measurement

At the output, the noise pedestal in the notch tends to fill due to the non-linearity of the PA. The depth of the notch at the output of the PA as shown in the Figure 2.10 is a measure of the NPR.

#### 2.2.2 Efficiency measurement

The efficiency of an amplifier is a measure of how effectively DC power is converted to RF power. The efficiency is a critical factor in power amplifier design, especially in a battery operated mobile devices. Different terms are used to describe the efficiency. Some of the most common definitions are presented below:

#### 2.2.2.1 Drain Efficiency

Drain efficiency is defined as the ratio of RF output power to dc input power.

$$\eta = \frac{P_o}{P_{dc}} \tag{2.5}$$

It does not take into account the RF input power. So, in the case of a RF amplifier with low gain this is not a convincing measure for efficiency.

#### 2.2.2.2 Power Added efficiency (PAE)

The definition of power added efficiency includes the effect of the drive power and gives a reasonable indication of power amplifier performance even when the gain is not high. The PAE is defined as

$$PAE = \frac{P_o - P_{IN}}{P_{dc}} = \frac{P_o - \frac{P_o}{G_p}}{P_{dc}}$$

(2.6)

where  $G_p = \frac{P_o}{P_{IN}}$  is the power gain

The PAE is most useful for constant amplitude signals.

#### 2.2.2.3 Overall efficiency

Overall efficiency is an alternative definition of PAE which also includes the effect of drive power.

$$\eta_{OVERALL} = \frac{p_o}{p_{dc} + P_{IN}} = \frac{P_o}{P_{dc} + \frac{P_o}{G_p}}$$

(2.7)

Overall efficiency is always positive, whereas PAE can be negative if the amplifier gain is less than 1.

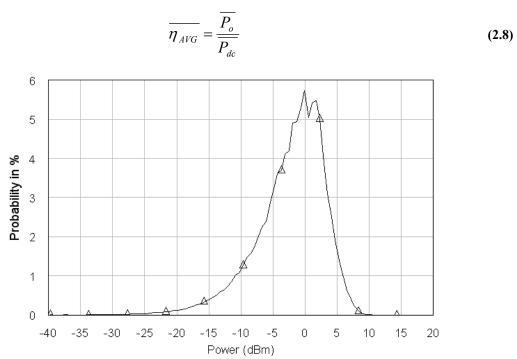

#### 2.2.2.4 Average efficiency

The above three definitions of efficiency are for a sinusoidal input and output (constant-envelope) signal. For most power amplifiers, the efficiency is highest at the peak output power and decreases as output/input decreases. However, most of the time power amplifiers operate far below the peak output power when amplifying a digitally modulated signal with high peak to average ratio as illustrated in Figure 2.11. When the envelope of the input signal is time-varying (non-constant), the efficiency is also a time-varying. So, a good method to measure the performance of the power amplifier is the average efficiency. It is the ratio of the average output power to the average dc input power.

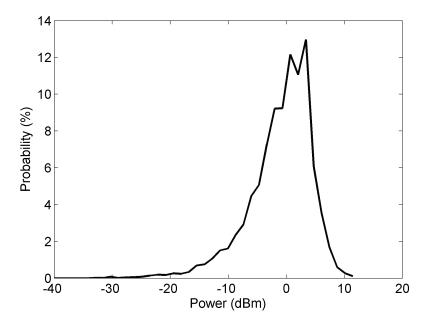

Figure 2.11 Probability distribution of output power occurrence in IEEE 802.11a/g signal

The average input and output power can be calculated as [6]

$$\overline{P_i} = \int_{0}^{P_{out,max}} P_{dc}(P_{out}) PDF(P_{out}) dP_{out}$$

(2.9)

and

$$\overline{P_o} = \int_{0}^{P_{out,\text{max}}} PDF(P_{out}) dP_{out}$$

(2.10)

Where PDF( $P_{out}$ ) is the probability that the amplifier will have an output power  $P_{out}$  and  $P_{dc}(P_{out})$  is the dc input power required at  $P_{out}$ .

Average efficiency is very useful in a case that is precisely formulated. It is the measure of how effectively the PA converts the stored energy in the battery into transmitted energy. So, it is directly related to the battery life in mobile handsets. However, it does not take peak current or power into account.

# 2.3 Basic Linear and Switch Mode Power Amplifiers

The previous section described several ways to quantify linearity and efficiency performance of power amplifiers. There is a fundamental tradeoff between linearity and efficiency in a standalone power amplifier, depending on its class. This section briefly discusses different classes of power amplifiers.

Power amplifiers are generally classified based on the circuit configuration and the conduction angle into different classes such as A, AB, B, C, D, E, F and so on. Normally these classes of PAs can be placed in two categories: Linear Mode and Switch Mode PAs. In linear mode PAs, the device normally acts as a transconductor. The relationship between input and output, however, may not be linear. In switch mode PAs, the device acts as a switch.

#### 2.3.1 Linear mode Power Amplifiers

The amplifier classes in this mode are differentiated based on the conduction angle, which is defined as the period at which the power device is conducting. Class-A, -B, -AB and -C belong to this category. Figure 2.12 shows the basic circuit topology for a linear mode power amplifier. By varying bias voltages and input drive power, the conduction angle can be chosen between 0 and 360°. The corresponding classes are defined as:

- Class-A amplifiers, if the conduction angle =360°.

- Class-B Power Amplifiers, if the conduction angle=180°.

- Class-AB Power Amplifiers, if 180°< conduction angle< 360°.

- Class-C power Amplifiers, if the conduction angle <180°.</li>

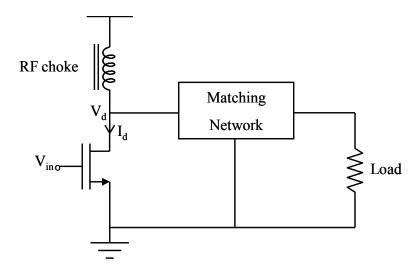

Figure 2.12: Basic Circuit of single-ended class-A, B, AB, or C amplifier

#### **Class-A Power Amplifiers**

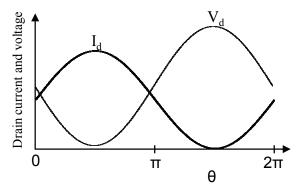

In a class-A power amplifier, the power device is biased such that the transistor remains in the transconductance region during the entire RF cycle, which means the conduction angle is 360°. As a result, class-A power amplifiers have the highest linearity and power gain compared to other amplifier classes. However, due to the bias point in the middle of the transconductance region of the I-V curves, a large quiescent current flows into the device resulting in huge power dissipation. The theoretical maximum power efficiency is 50%. Drain current and voltage waveforms of an ideal class-A amplifier [7], [8] are shown in Figure 2.13.

Figure 2.13: Ideal drain current and voltage waveforms of a class-A power amplifier In summary, Class-A PAs have high linearity, high gain, wideband operation, high frequency operation and poor efficiency.

### **Class-B Power Amplifiers**

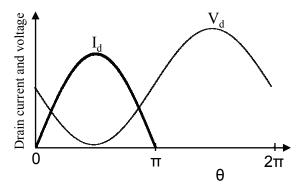

In class-B operation the gate of the power transistor is biased at the threshold voltage (zero quiescent current) so that the drain current flows during only one half of the input

sinusoidal signal, resulting in a conduction angle of 180 °. Figure 2.14 shows the drain current and voltage waveforms of an ideal clas- B amplifier.

Figure 2.14: Ideal drain current and voltage waveforms of a class-B power amplifier

Mostly, class-B amplifiers are designed in push-pull configuration so that each transistor conducts for each half cycle and the two drain currents add together to produce a sine-wave output. But linearity, output harmonic content, and intermodulation distortion are not as good as in class-A. However, the maximum efficiency of a class-B amplifier is considerably higher, theoretically 78.5%. In practice, to reduce the crossover distortion, the transistor is biased at a small quiescent current, typically 1-10% of the peak drain current. Thus, practical devices in principle operate in class-AB.

#### **Class-AB Power Amplifiers**

A class-AB power amplifier is a good compromise between a class-A and a class-B amplifier and is biased such that the conduction angle is between 180 ° and 360 °. The linearity of class-AB amplifiers is close to that of class-A amplifiers while the efficiency is close to that of class-B amplifiers. The bias point for those amplifiers is selected depending on the linearity and efficiency requirements.

Figure 2.15: Ideal drain current and voltage waveforms of a class-AB power amplifier

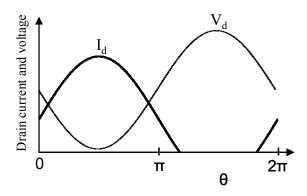

#### **Class-C Power Amplifiers**

The gate of the power transistor in a class-C power amplifier is biased below the threshold so that the transistor is active for less than half of the RF cycle. The efficiency is higher than that of class-A, B, and AB. The theoretical maximum efficiency reaches towards 100% by decreasing the conduction angle toward zero. But at the same time, output power decreases towards zero. This class of PAs is highly non-linear in high efficiency operation. One main advantage of class-C amplifier in comparison to switch mode PA is that the output amplitude varies with the input amplitude. This means the class-C amplifier can be used to amplify variable envelop signals, keeping the possibility to get high efficiency without varying the supply voltage [9]. For switch mode PAs, the only way to control the output power is by varying the supply voltage.

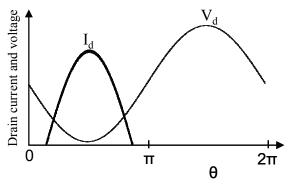

Figure 2.16: Ideal drain current and voltage waveforms of a class-C power amplifier

#### 2.3.2 Switched Mode Power Amplifiers

In switch mode power amplifiers the device acts as a switch. Those power amplifiers are highly non-linear and known for high efficiency. The theoretical maximum efficiency is 100%.

#### **Class-D Power Amplifiers**

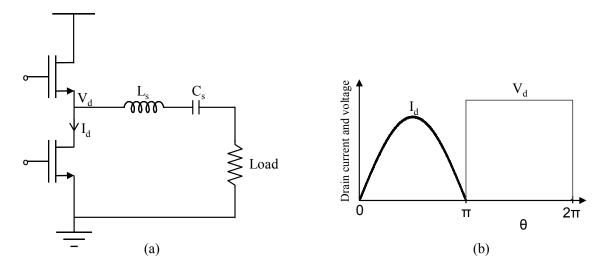

Figure 2.17(a) shows a typical class-D amplifier circuit. Class-D amplifiers use two active devices which act as a two pole switch that connect the load network to ground and supply alternately. With this push-pull operation, a rectangular voltage waveform is generated at the drain. The LC tank circuit passes only the fundamental components to the load. Figure 2.17(b) shows the drain current and voltage waveform in an ideal class-D operation.

The ideal maximum efficiency of class-D PA is 100%. However in practice it suffers losses from ON-resistance, finite switching time and drain capacitance. Class-D amplifiers are used extensively in audio applications, but are seldom used above VHF due to the high switching loss.

Figure 2.17: a) Class-D amplifier and b) its waveforms at the output node

#### **Class-E Power Amplifiers**

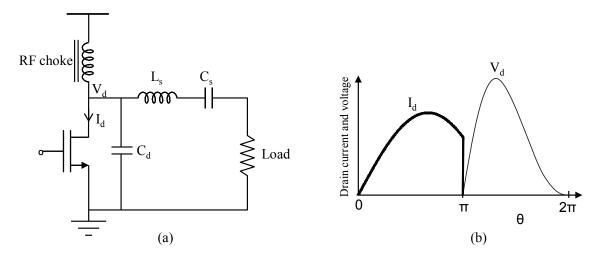

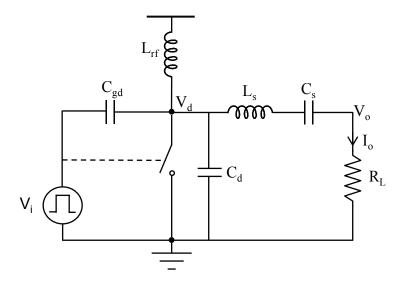

The basic schematic of a class-E amplifier is shown in Figure 2.18(a). It uses the idea of soft switching and usually employs a single transistor as a switch. The class-E PA tries to force the voltage across the output node  $(V_d)$  to zero with zero slope at the instant when the switch is closed (as shown in Figure 2.18(b)) so that there is no switching loss [10]. The most common matching network consists of a series tuned LC circuit and shunt capacitor across the switch. One of the big advantages of this amplifier is that the drain-source capacitance of the transistor can be used as the one of the circuit component in the matching network. So the transistor's drain-source capacitance is no longer a source of power loss as in the case of class-D but becomes an important part of the circuit operation. For this reason, the class-E amplifier is used in very high frequency applications.

Figure 2.18: a) Class-E power Amplifier and b) its waveform at the output node

#### **Class-F Power Amplifiers**

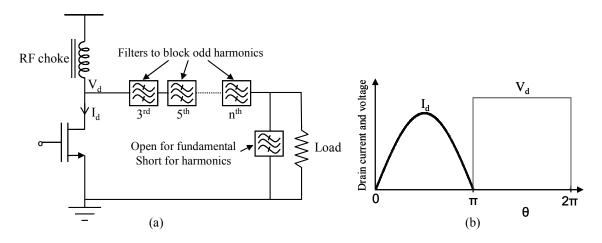

The class-F PA is distinguished by the matching network which consists of multiple harmonic resonant filters. For ideal operation of Class-F amplifiers as shown in Figure 2.19(a), the matching network should be such that it blocks all the odd harmonics, and shorts all the even harmonics. The addition of harmonic components shapes the drain waveforms to square at the output of the active device as shown in Figure 2.19(b), thus eliminating loss in the switch. This makes class-F amplifiers suitable for high frequency operation. However in practical applications, the harmonic tuning is applied only up to the third or fifth harmonic, to reduce the matching network circuitry. Consequence of this is a little degradation in efficiency due to some overlap between the drain current and voltage.

Figure 2.19: a) Ideal class-F power amplifier and b) its waveforms at the output node

#### Conclusion

Linear modes PAs such as class –A, -B, - AB have high linearity performance and can be used to amplify a variable envelope signal without adding other linearization schemes. But those amplifiers have poor efficiency. Classes-C, -E and -F have very high potential to get high efficiency in RF frequencies but suffer from poor linearity. This illustrates the efficiency-linearity trade-off in traditional power amplifiers.

# 2.4 Efficiency Enhancement Techniques

This section describes some of the efficiency enhancement techniques that defy the traditional efficiency-linearity trade-off in power amplifiers. These techniques try to enhance the efficiency at low envelope power, thus increasing the average efficiency.

#### 2.4.1 Doherty Amplifier

The Doherty technique [11], first proposed in 1936 for use in high-power broadcast transmitters, is the simplest efficiency boosting technique. The Doherty configuration

uses an active load-pull technique. The detail about the load-pull technique is explained in [12]. Figure 2.20(a) shows the schematic of the active load-pull technique. According to circuit theory, Gen1 sees the load resistance of  $R_L$  if Gen2 doesn't supply any current. When Gen2 starts to supply a current proportional to  $I_1$ , the resistance seen by the Gen1

will be:

$$R_1 = R_L \left( 1 + \frac{I_2}{I_1} \right)$$

As  $I_2$  increases, the resistance,  $R_1$ , seen by the Gen1 also increases. So the resistance seen by Gen1 can be modified according to the current supplied by the Gen2. Similarly, Gen2

sees a resistance of:  $R_2 = R_L \left(1 + \frac{I_1}{I_2}\right)$ Gen1

Gen2

Figure 2.20: (a) Schematic of active load-pull technique (b) with impedance inverter illustrating the configuration of Doherty amplifier

(b)

Similarly in Figure 2.20(b), an impedance inverter is added so that the impedance seen by the Gen1 decreases as the current supplied by the Gen2 increases.

#### **Operation of the Doherty Amplifier**

(a)

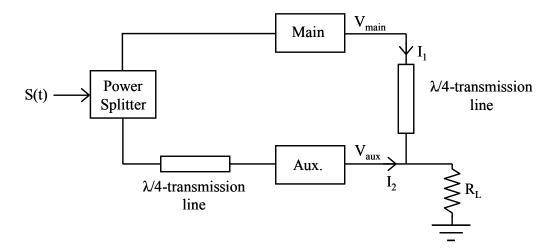

The simplest configuration of a Doherty circuit (two-way) consists of two amplifiers; "main" or "carrier" amplifier and the "auxiliary" or "peaking" amplifier. The amplifiers are connected in parallel with a quarter wave transmission line (impedance inverter) as shown in Figure 2.21 so that the configuration is equivalent to Figure 2.20(b) with the Gen1 as the main and the Gen2 as the auxiliary amplifier.

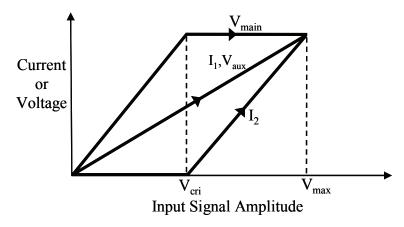

The basic concept of the Doherty amplifier is to allow the main amplifier to operate at the maximum efficiency (peak power) while allowing the auxiliary amplifier to deal with the modulation peaks. When the input drive is low the auxiliary amplifier is shut-down and the main amplifier operates in the linear mode as shown in Figure 2.22. If a class-B PA is used as the main amplifier and the class-C as auxiliary amplifier, the class-C is off because signal is too small. As the input drive increases, the main amplifier starts to saturate and the auxiliary amplifier starts to supply current. This turn-on point of the auxiliary amplifier is called the *transition point*. At the transition point, the efficiency of the overall system becomes high.

Figure 2.21: Schematic of Doherty Amplifier

Figure 2.22: Current and Voltage at the output of the main and auxiliary amplifier

Above the transition point, the impedance seen by the main amplifier reduces due to the current supplied by the auxiliary amplifier. Because of this "load pulling" effect, the main amplifier delivers more current to the load and operates as a controlled voltage source while it is saturated. On the other hand, the auxiliary amplifier takes over operation as a linear amplifier. In this region both devices contribute to the output power. At the peak envelop power the auxiliary amplifier is also saturated and the efficiency of the overall system becomes again high. In this way, the two amplifiers give a composite linear power response, maintaining the efficiency close to maximum, typically down to the 6dB back-off point. (Note: typically for a two-way Doherty amplifier, the transition point is chosen at 6dB below the composite maximum power). Figure 2.22 shows the current and the voltage characteristic of the main and the auxiliary amplifier for the whole range of input voltages.

#### Performance of the Doherty Amplifier

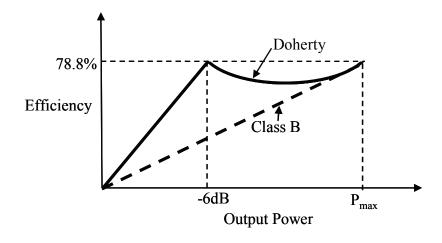

The overall efficiency characteristic of the Doherty amplifier as a function of power back-off is shown in Figure 2.23.

Figure 2.23 Efficiency versus power back-off of Doherty amplifier (solid line) and class-B amplifier (dotted line)

If a class-B PA is used as the main amplifier and the class-C as auxiliary amplifier, the theoretical maximum efficiency is 78.8%. The efficiency is close to the maximum throughout the upper 6dB. The small dip in the efficiency in between the transition point and full power (i.e. at 6dB back-off) is due to the lower efficiency of the auxiliary amplifier which operates in back back-off.

#### **Disadvantages**

A Doherty amplifier is very narrow band because of the use of quarter-wave transmission lines and the requirements of accurate phase matching between the two paths. Another drawback is the poor IMD performance mainly due to the low biasing of the auxiliary amplifier. However, other linearization scheme can be implemented to improve the linearity in the Doherty amplifier but this will add the complexity.

| Region of operation     | Main Amplifier     | Auxiliary amplifier | Overall Efficiency |  |  |

|-------------------------|--------------------|---------------------|--------------------|--|--|

| Below the transition    | Operates in linear | Shut down           | poor               |  |  |

| point                   | mode               |                     |                    |  |  |

| At the transition point | Just saturated     | Just turn -on       | maximum            |  |  |

| Above the transition    | Saturated          | Operates in linear  | Close to maximum   |  |  |

| point and below the     |                    | mode                |                    |  |  |

| full power              |                    |                     |                    |  |  |

| At Full Power           | saturated          | saturated           | maximum            |  |  |

Table 2.1: Summary of the operation of the Doherty Amplifier

#### **Improved Doherty Amplifier**

Various techniques are employed to improve the performance of Doherty amplifiers. In [13], [14] envelop tracking is used to vary the bias point of the auxiliary amplifier according to the envelope of the input signal for high efficiency and linearity of the Doherty amplifier. Instead of choosing the transition point at 6dB back-off, [15] implemented the Doherty technique with the transition point at 10-dB back-off. To handle the large power back-off that means to amplify the variable envelope signal with large PAPR, the number of paths can be increased. The N-way Doherty amplifier is basically paralleling one carrier amplifier and N-1 numbers of auxiliary amplifiers. Two, three and four-way structure are implemented in [16], [17] which have the transition point at 6-, 10- and 12-dB output power back-off. Similarly one auxiliary amplifier and a number of main amplifiers can also be used; this structure is called the multi-stage Doherty amplifier. This configuration has two main advantages; i) the range of power back-off increases and ii)the overall efficiency characteristic of the Doherty system becomes close to ideal due to increase in the number of transition points, as the number of stages increases. This is shown in [5]. A Doherty amplifier with improved load matching using a load modulation technique is presented in [18].

#### **Conclusion**

Predominantly Class-A or -AB or -B is used as the "main" amplifier and class-C is used as the Auxiliary amplifier. However, switch mode PAs can also be used as the main [19] if the PER or exact possible power back-off is known and the transition point is chosen according to that. The performance of the Doherty topology mainly depends on the class of operation of the two amplifier blocks. Using the Doherty technique, the efficiency at back-off can be kept close to that in saturated condition.

# 2.4.2 Outphasing Amplifier

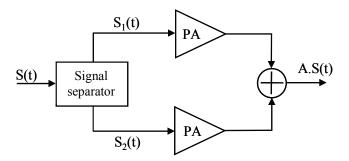

The Outphasing technique was first introduced in 1930s by Chireix. This technique is also named LINC (Linear Amplification Using Nonlinear Components), when it came into use at microwave frequencies in 1970's. In this technique, the envelope varying signal is first decoupled into two phasors with equal amplitudes. The phasors are then amplified separately in highly power efficient nonlinear amplifiers and finally the originally AM component is recovered by recombining those two signals.

Figure 2.24 LINC PA block diagram

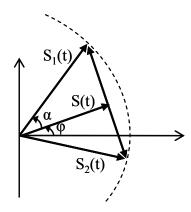

Figure 2.25 Vector diagram showing the input signal and the constant amplitude signals at the output of the signal separator

To understand this principle in more detail consider a variable envelope signal

$$S(t) = A(t)\cos(\omega_c t + \varphi)$$

(2.11)

As shown in Figure 2.25, this signal can decomposed into two signals having equal amplitude:

$$S_1(t) = \cos(\omega_c t + \varphi + \alpha) \tag{2.12}$$

and

$$S_2(t) = \cos(\omega_c t + \varphi - \alpha) \tag{2.13}$$

Such that

$$2S(t) = S_1(t) + S_2(t)$$

(2.14)

Where

$$\alpha = \cos^{-1}[A(t)]$$

The key elements in the outphasing PAs are the phase modulator (signal separator) and the output power combiner. The signal separator decomposes the incoming signal vector (S(t)) of any magnitude and phase into two vectors  $(S_1(t))$  and  $S_2(t)$  with constant magnitude. A DSP is assumed to be the best choice for signal component separation. However, an analog signal component separator is also promising [20]. After amplification the two signals are added by using the output power combiner.

As the outputs of the PAs in the two paths are about to phase cancel in order to generate a low amplitude output, the dc power drawn by the pair of the saturated PA is also reduced because of the increase in equivalent load resistance seen by each device. This load pulling effect preserves the high efficiency during low amplitude input. This is the key feature of out-phasing PAs.

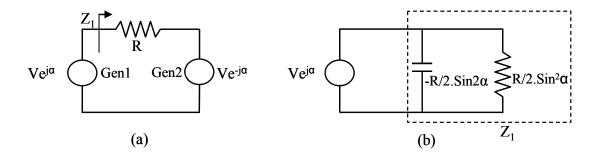

Figure 2.26: a) Output schematic of out-phasing amplifier, b) Equivalent circuit at generator 1

Figure 2.26(a) shows the schematic of a possible RF output connection and Figure 2.26(b) shows the equivalent load seen by the Gen 1 due to the effect of the out-phasing modulation. It can be clearly seen that the phase difference between the two generators is causing a reactive component at the load. As  $\alpha$  increase towards 45° to reduce the output envelope amplitude, the load seen by the generator becomes more reactive, causing lower efficiency. Chireix proposed the use of an additional reactive component across the devices to compensate the out-phasing reactance. However, the compensation can be done at only one value of the phase angle  $\varphi$  and of course the efficiency is again the maximum at this point.

## Disadvantages

• To achieve potentially high efficiency, it is desirable to use switch-mode power amplifiers such as class-E for the implementation of the component amplifiers. Unfortunately, the class-E PA is not well-suited for outphasing system because of varying load impedance with lossless power combining [21], [22]. The zero voltage switching characteristic is only valid for the fixed load. So, the class-E power amplifiers are best suited with lossy power combiner such as Wilkinson combiner that provides the isolation between the amplifiers output with fixed input impedance. However the power combining is inevitably lossy as only the fraction of the output power of class-E appears at the combiner output and the rests is dissipated across the combiner's resistor, depending on the relative phase of the amplifiers.

Interestingly, class-D amplifier is attractive for outphasing implementation [21]. In the class-D case, when the phase of the load current is different than that of the voltage, there is a positive and negative current flow through the switches. So, the current is drawn from the supply and return back to it in the same cycle through the high-side switch. For a phase difference of 90° between the load current and voltage, which means for zero output power of the outphasing system, the average current drawn from the supply is zero. This is an attractive property to achieve high efficiency at low output power. However, the class-D amplifier suffers from high switching loss from its output capacitance for high frequency applications.

- The output power is extremely sensitive to the out-phasing angle especially for low output amplitude and hence the phase mismatch between the two paths (in some cases 1° of out-phasing angle could result -40dB variation in the output power [12]). So this technique is not so suitable when a large back-off is needed. Consequently, this technique is best suited for a modulation scheme that avoids zero crossing like π/4-shifted-DQPSK.

- Signal separation is complex

#### Conclusion

Reactive compensation is the key element to improve the average efficiency of an outphasing PA. But even without reactive compensation the efficiency characteristic is attractive. An out-phasing technique using DSP phase control in baseband (LINC transmitter) is popular in linear applications. Due to the high sensitivity to the phase imbalances, this technique is not so suitable for signals with high peak-to-average power ratio.

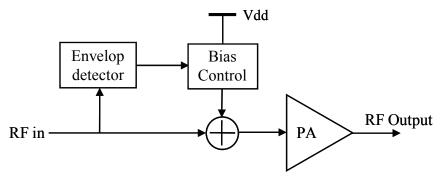

#### 2.4.3 Adaptive Bias

The adaptive bias technique was primarily proposed to increase the power added efficiency of class-A amplifiers during large back-off. In this technique the bias level of the amplifier is varied with the envelop level to reduce the amount of dc current drawn from the supply during back-off. The operation of the adaptive bias scheme is shown in Figure 2.27. The gate bias of the PA is varied proportionally to the signal from the envelope detector.

Figure 2.27: Schematic of the adaptive bias control

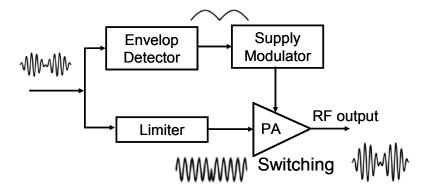

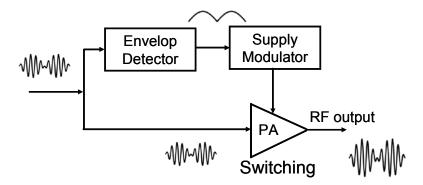

# 2.4.4 Envelope Elimination and Restoration or Polar Modulation

The Envelop Elimination and Restoration (EER) technique [23] was first proposed by Kahn in 1952 and also known as Polar modulation technique. In its classic structure as shown in Figure 2.28, the amplitude and phase information are separated from the input signal using an envelope detector and a limiter. The phase modulated signal is then amplified by a highly efficient amplifier such as class-C, -D, -E, or -F. The envelope

(amplitude information) is used to modulate the power supply of the final RF PA to restore the signal envelope at the output.

Figure 2.28: Schematic of EER/Polar modulation technique

Since switch mode amplifiers can be used both in the supply modulator as well as in the final power amplifier, this technique has a potential to achieve high efficiency, theoretically 100%. Details about this technique will be discussed in chapter IV.

#### 2.4.5 Envelope Tracking

The absence of a limiter before the RF PA is the main difference between an Envelope Tracking (ET) and the EER architecture. As a result, the RF drive contains both the amplitude and the phase information and the burden of linearity lies on the RF PA itself. This technique is also called "dynamic drain/collector biasing".

Figure 2.29: Envelope tracking architecture

As shown in Figure 2.29, the envelope detector extracts the envelope information from the RF input signal and uses it to control the collector/drain voltage of the PA through a supply modulator. The supply modulator dynamically adjusts the RF PA with just sufficient supply voltage to reduce the dc power consumption at low power levels, thus increasing the average efficiency of the whole system. Other advantage is that the linearity of the system is less dependent on the bandwidth of the supply modulator. In

summary this technique is much simpler to implement than an EER, where each block has tough requirements.

Some disadvantages of Envelope tracking techniques are:

- The theoretical maximum average efficiency is not as high as for the EER technique because of the use of a linear mode PA. Average efficiency is directly proportional to the peak to average power ratio.

- Mismatch of the delays between the two paths (supply and signal paths) degrades the linearity, though not as much as with EER.

- The power gain of the PA decreases as the supply voltage is reduced.

#### 2.4.6 Summary of Efficiency Boosting Techniques

Various efficiency boosting techniques were summarized in this section. The Doherty technique is based on an active load-pull technique. Basically, the efficiency boosting techniques described above are mainly based on "load pulling" and "Vdd pulling" so that the output of the PA swings from rail-to-rail. The Doherty and Chierex techniques use load pulling while ET and EER are based on Vdd pulling.

The basic concept of the Doherty amplifier is to allow the main amplifier to operate at the maximum efficiency (peak power) while allowing the auxiliary amplifier to deal with the modulation peaks. So the overall efficiency remains high during back-off as well. The Chierex/LINC architecture has the exciting feature that it first divides the varying envelope signal into two constant envelope signals which are then amplified by highly efficient non-linear amplifiers. However, the signal separation and the recombination after amplification are a difficult task. The Envelope Elimination and Restoration technique was also briefly discussed in this chapter. The main feature of this technique is the theoretical 100% efficiency regardless of the power back-off. Each block in the EER topology has strict requirements to satisfy the linearity of the overall PA system. A less aggressive technique is Envelope Tracking. In ET, the burden of linearity lies on the final PA itself. So the final PA must be a linear PA and hence the average efficiency is not as high as the EER technique.

# 2.5 Output Filtering

No matter which kind of amplifier is used, filters at the output are considered inevitable to suppress the harmonic products generated by non-linearities. Suppression of the harmonics avoids signal interference with other devices operating in a different frequency band. The output matching network of a power amplifier attenuates the harmonics significantly depending on the type and configuration as it is mostly narrowband. So the matching network itself acts as a filter. A separate RF filter after the matching network might also be needed to further suppress the harmonics. Nevertheless, the output filter (matching network and the additional filter if present) in all wireless transmitters has to make sure that the harmonics are suppressed to the acceptable level.

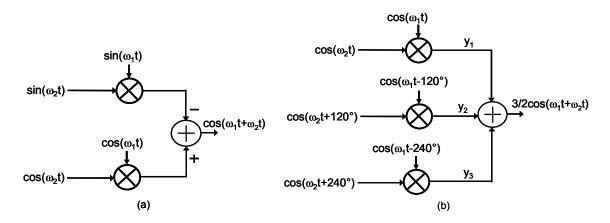

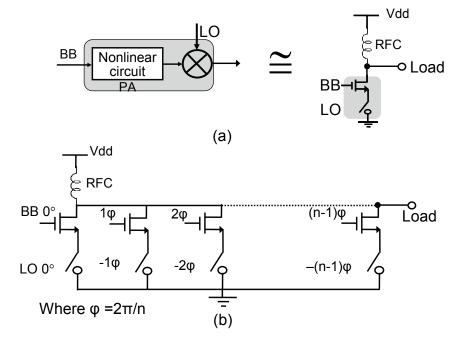

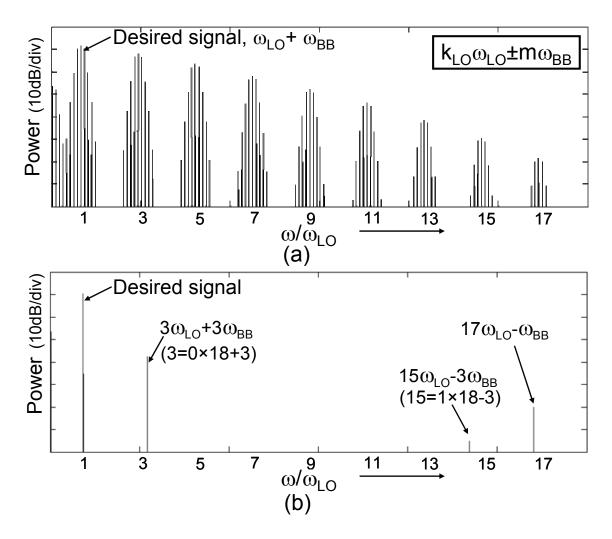

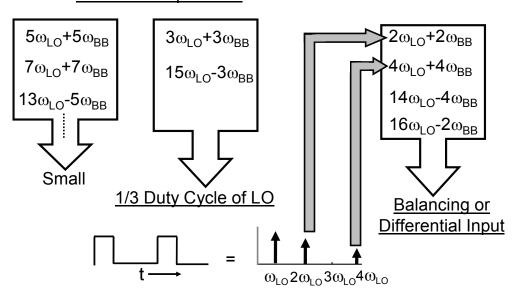

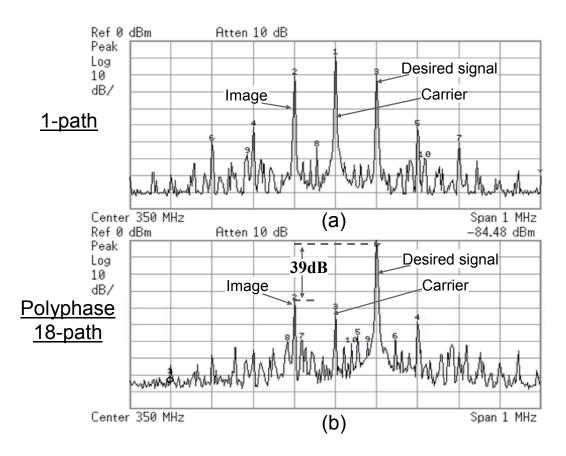

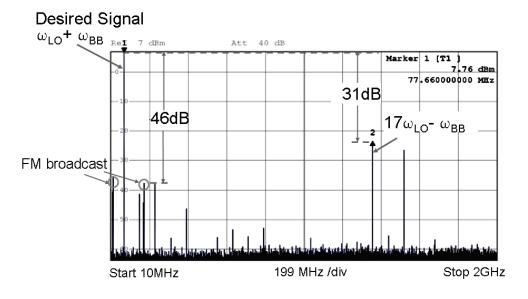

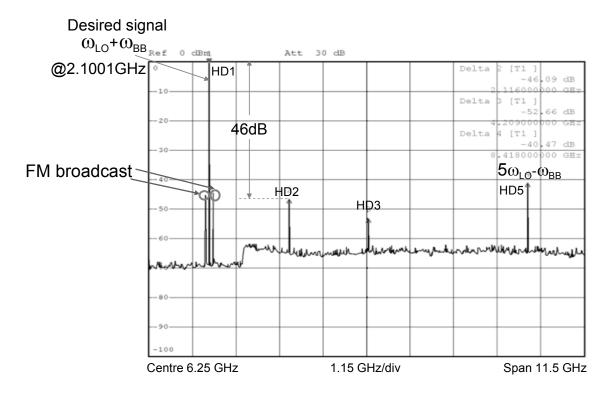

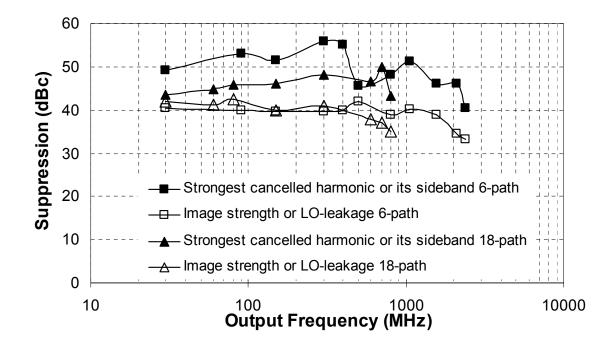

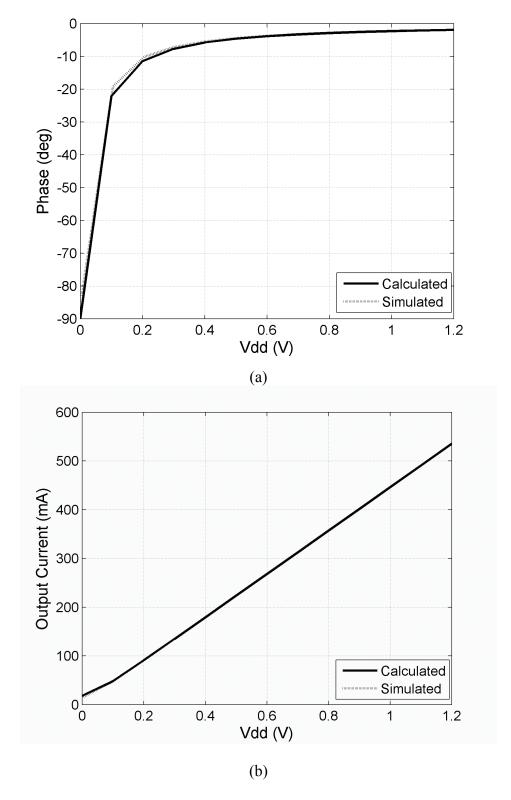

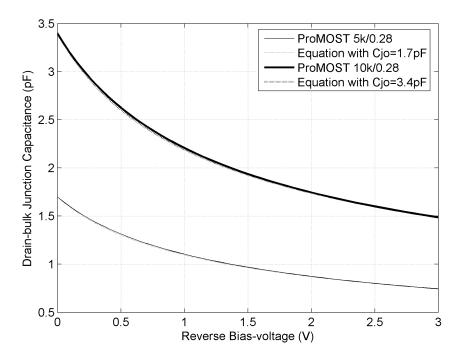

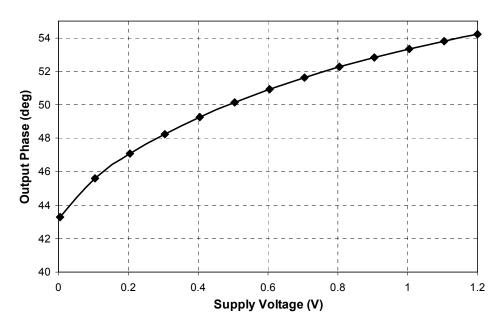

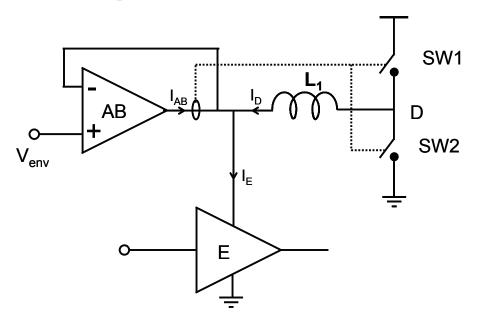

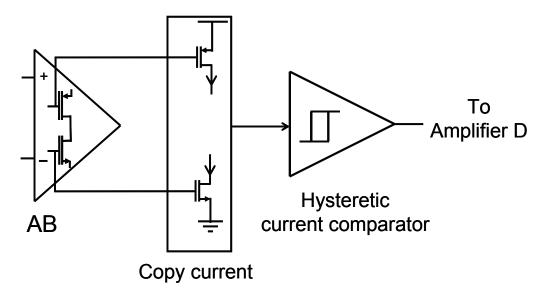

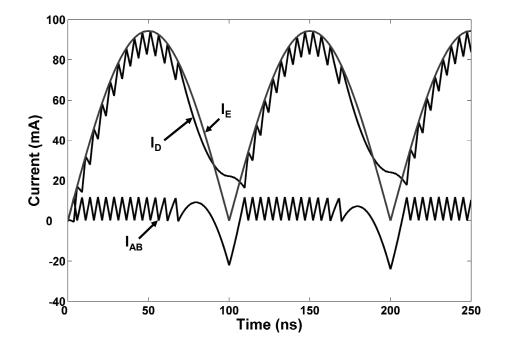

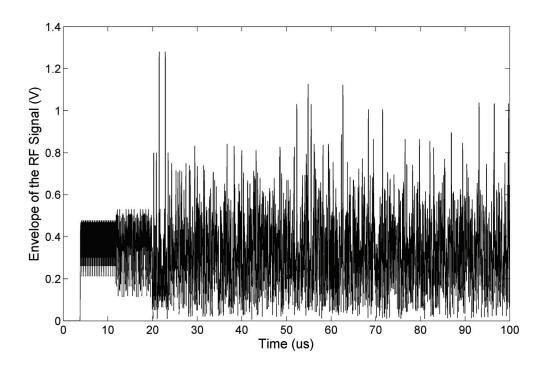

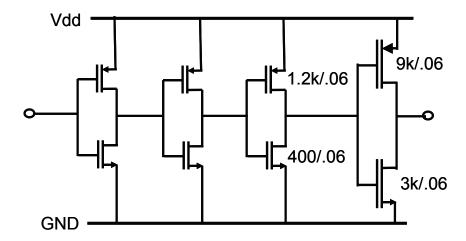

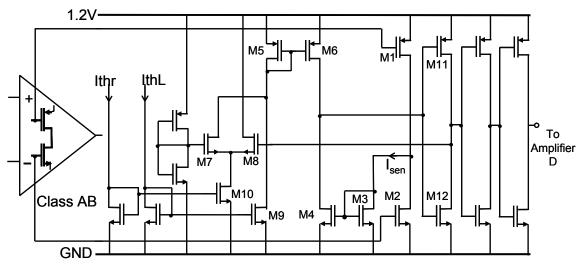

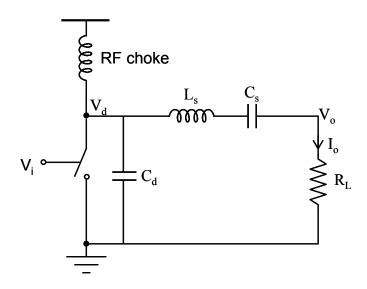

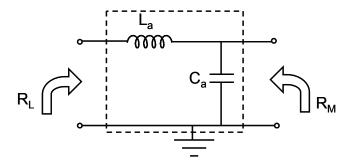

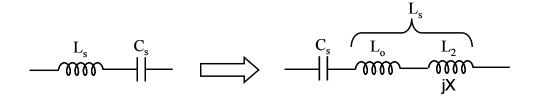

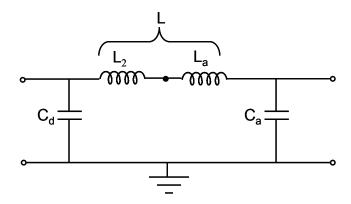

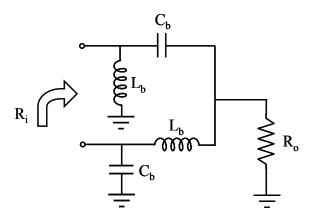

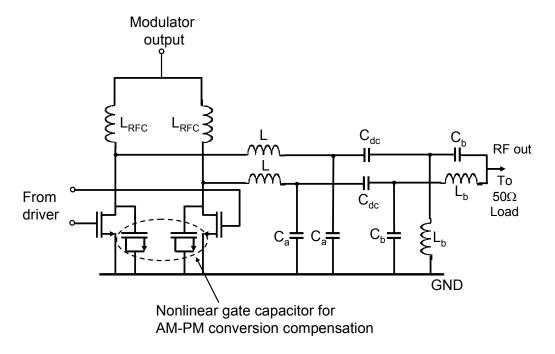

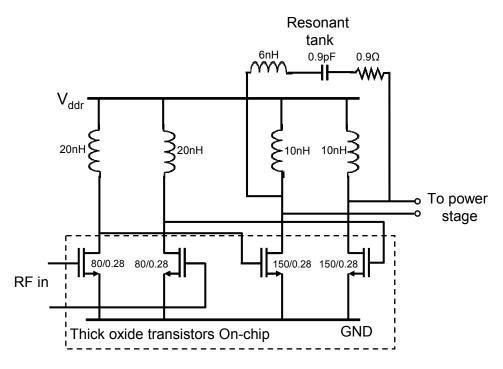

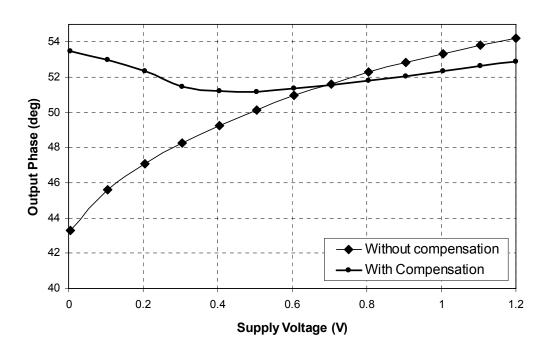

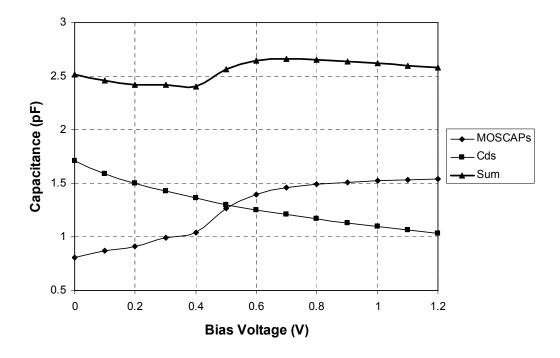

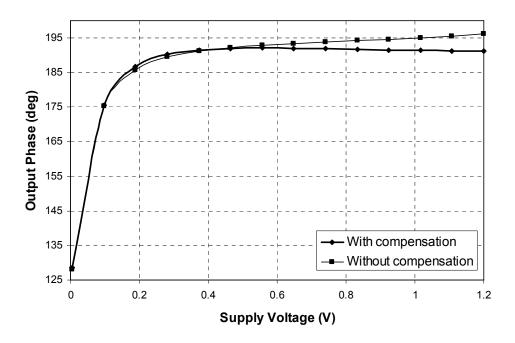

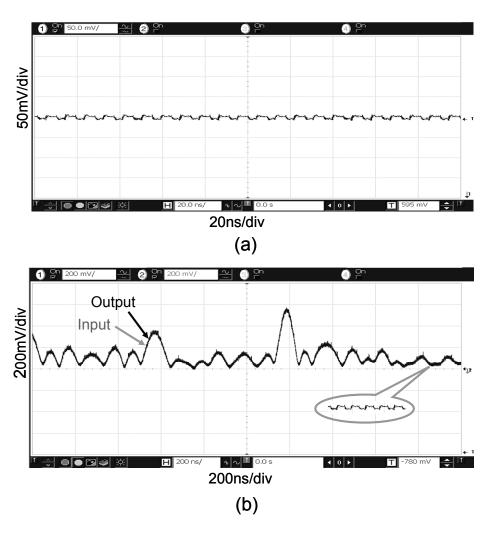

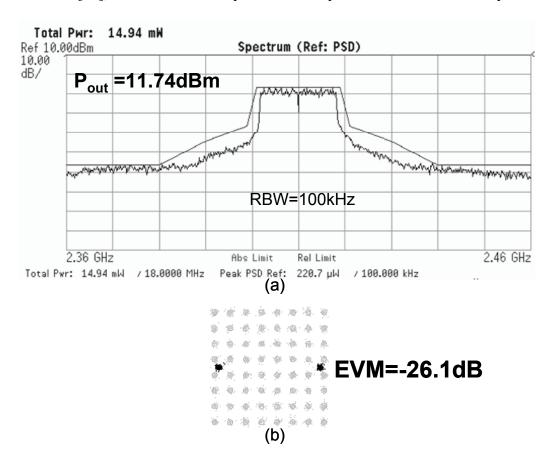

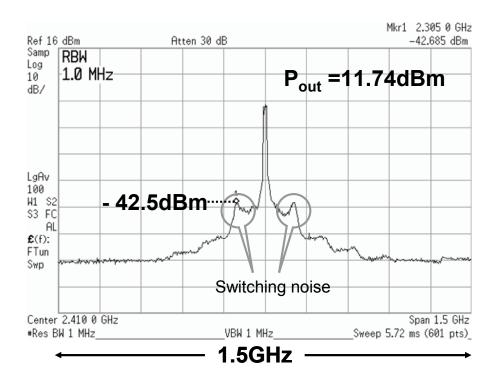

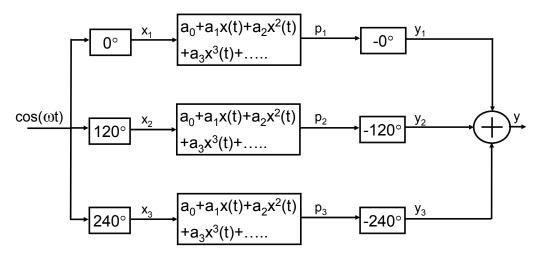

Main consequence of the output filtering is that dedicated hardware or filters are needed for each standard. Nonetheless, in a typical multi-standard transmitter, with multiple narrow-band power amplifiers which are limited in bandwidth by dedicated filters, each standard can have its own antenna or can be made selectable by a switch. With the ever increasing number of different standards to be supported, this architecture becomes increasingly unpractical and not an economical solution, as support for every new frequency band requires adding external dedicated components. So in future mobile communications, a flexible hardware is desired that can be used for different standards under software control. Such flexibility is envisioned in software-defined radio and cognitive radio system. One way to achieve this is to use tunable filters. In [24], [25], [26], [27], a Micro-Electro-Mechanical-Systems (MEMS) switch is used to tune the filter to different frequency band. MEMS switches are an attractive option since they have high power handling capability and low insertion loss. However, it needs an especial packaging because MEMS switches are moving devices that are vulnerable to contamination from various environmental sources such as dust, moistures and gas vapors. This results in increase cost and size [28]. A circuit employing MEMS devices often reaches dozens or hundreds of square millimeters [24]. Furthermore, MEMS switch needs high excitation voltage (about 50V) which is not available in mobile phones and the 10 years life time reliability has not yet been proven for low cost MEMS solutions [28].